计算机组成原理4

实验过程:

RAM ROM引脚

RAM

随机存储器针脚:

sel(片选)

load data

clr

A

D

ROM

Sel引脚:

D 引脚:

A 引脚:

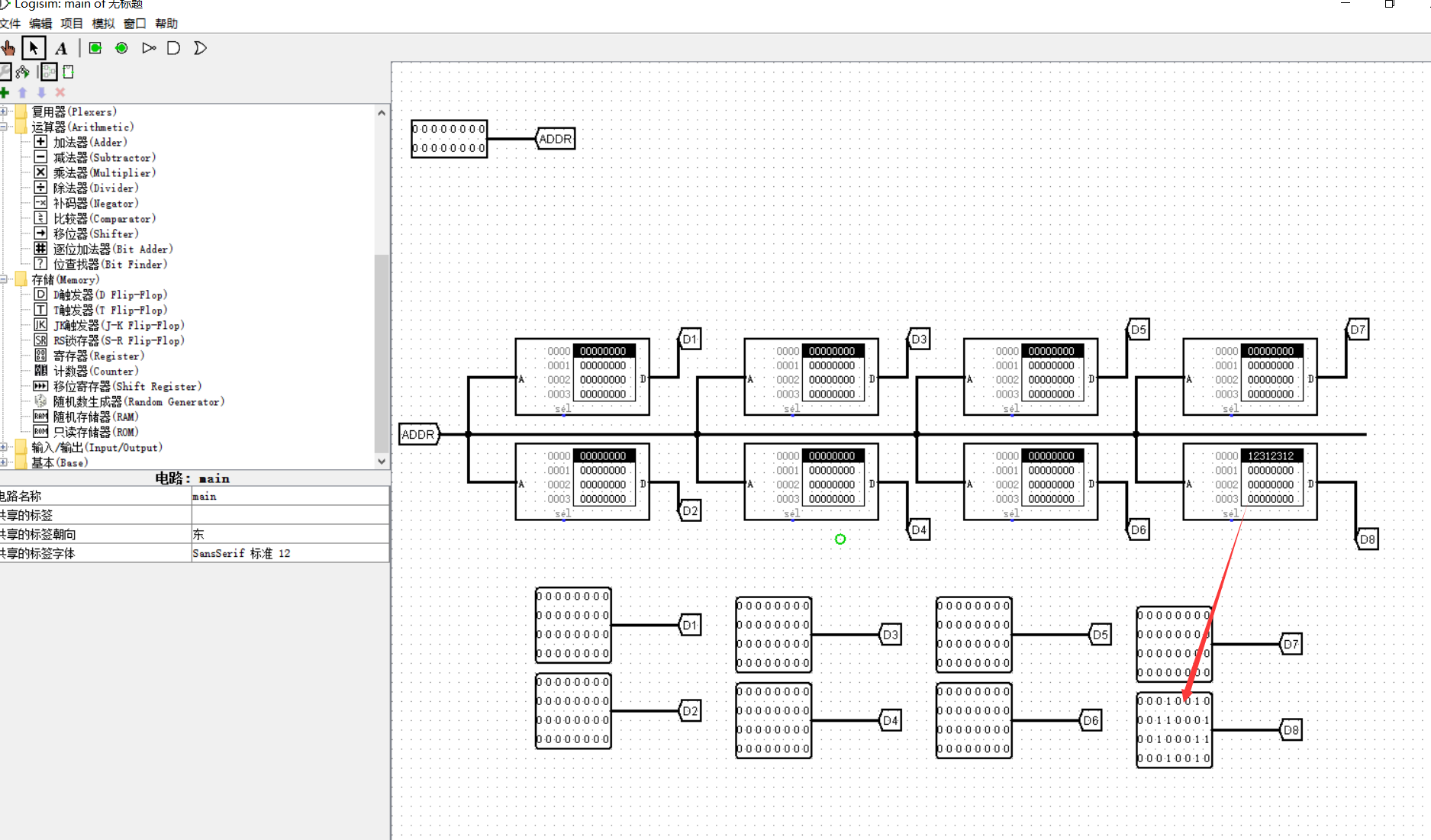

任务1:存储器位扩展

在这个任务中,我们将使用Logisim来创建一个存储器位扩展电路。位扩展是通过多个存储器器件来扩展字长的一种方式。我们将使用4个322位芯片来组成一个328位的存储器,并改变地址、设置片选sel和加载ld信号来模拟位扩展。

- 打开Logisim并创建一个新的电路。

- 在电路中添加4个322位的存储器芯片,并将它们连接在一起,以创建一个328位的存储器。设置每个存储器的地址范围,确保它们不重叠。

- 添加一个地址输入端口(Address BUS),一个片选sel输入端口,一个加载ld输入端口,以及一个输出端口。

- 连接地址输入端口到存储器的地址输入,并将片选sel和加载ld连接到相应的存储器控制端口。

- 使用Logisim的时钟源来改变地址、设置sel和ld信号,观察输出结果。

322 位芯片组成 328 位的存储器

32*2 地址是32个(有5个地址位,32个单元),数据位宽是2位(每个单元两个bit,也就是输出两个bit)

存储器选择5地址位宽 + 2数据位宽

任务2:存储器字扩展

利用logisim组件做如下电路

字扩展指的是增加存储器中字的数量。如下图⽤4个328位芯⽚组成1288位存储器。了解数据总线(Address BUS)和地址总线(Data BUS)概念和简单应用

- 打开Logisim并创建一个新的电路。

- 在电路中添加4个328位的存储器芯片,并将它们连接在一起,以创建一个1288位的存储器。设置每个存储器的地址范围,确保它们不重叠。

- 添加一个地址输入端口(Address BUS)和一个片选sel输入端口。

- 连接地址输入端口到存储器的地址输入,并将片选sel连接到相应的存储器控制端口。

- 使用Logisim来改变地址和片选信号,观察输出结果。

总地址位

7 6 5 4 3 2 1

<片选><-----地址------>

解码器

右边的针脚

加上load data 、 clear 线路

任务3:存储器字位扩展

存储器字位扩展(4片324位存储器位组成2片328位存储器字扩展为64*8位存储器)

- 打开Logisim并创建一个新的电路。

- 在电路中添加4个324位的存储器芯片,并将它们连接在一起,以创建2片328位的存储器。设置每个存储器的地址范围,确保它们不重叠。

- 添加一个地址输入端口(Address BUS)和一个片选sel输入端口。

- 连接地址输入端口到存储器的地址输入,并将片选sel连接到相应的存储器控制端口。

- 使用Logisim来改变地址和片选信号,观察输出结果。

两片合起来

6 5 4 3 2 1

<片选><-----地址------>

片选1

片选2

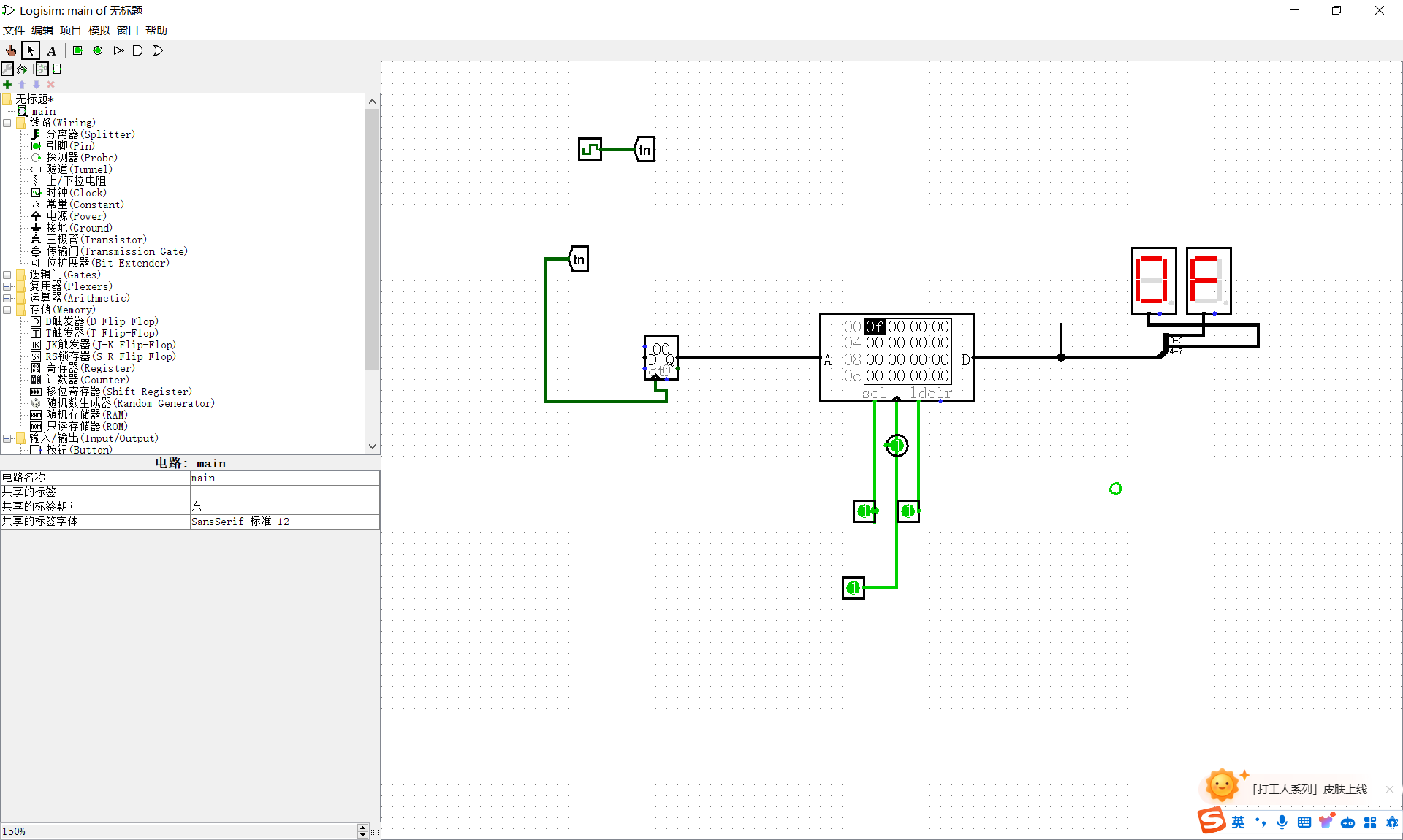

任务4:学号和成绩显示电路

完成如下学号、成绩显示电路(注:为降低难度,存储显示系统为十六进制,使用时不要输入十进制以外数据,直观上做十进制数据操作)

- 打开Logisim并创建一个新的电路。

- 添加一个只读存储器(Read-Only Memory,ROM)组件,并设置其大小和地址范围,以适应学号和成绩数据的存储。

- 添加一个地址输入端口和一个片选sel输入端口,并将它们连接到ROM。

- 添加一个显示组件,用于显示学号和成绩数据。

- 设置ROM加载镜像,读入相应的

学号和成绩文本文件。

先保存镜像,然后加载镜像

填入数据就行

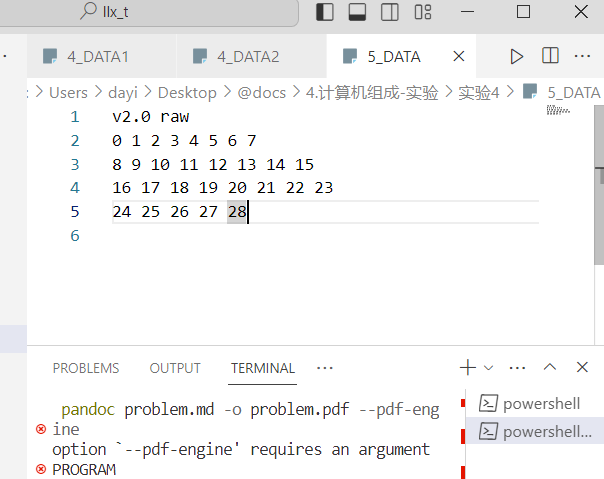

v2.0 raw

0 1 2 3 4 5 6 7

8 9 10 11 12 13 14 15

16 17 18 19 20 21 22

23 24 25 26 27 28v2.0 raw

90 91 92 93 94 95 96 97

98 99 a0 80 81 82 83 84

85 86 87 88 89 70 71 72

73 74 75 76 77 78 79 99

- 模拟电路运行,并通过更改地址来查看不同的学号和成绩数据。

CLK模拟:

这里100存了a0当做100分

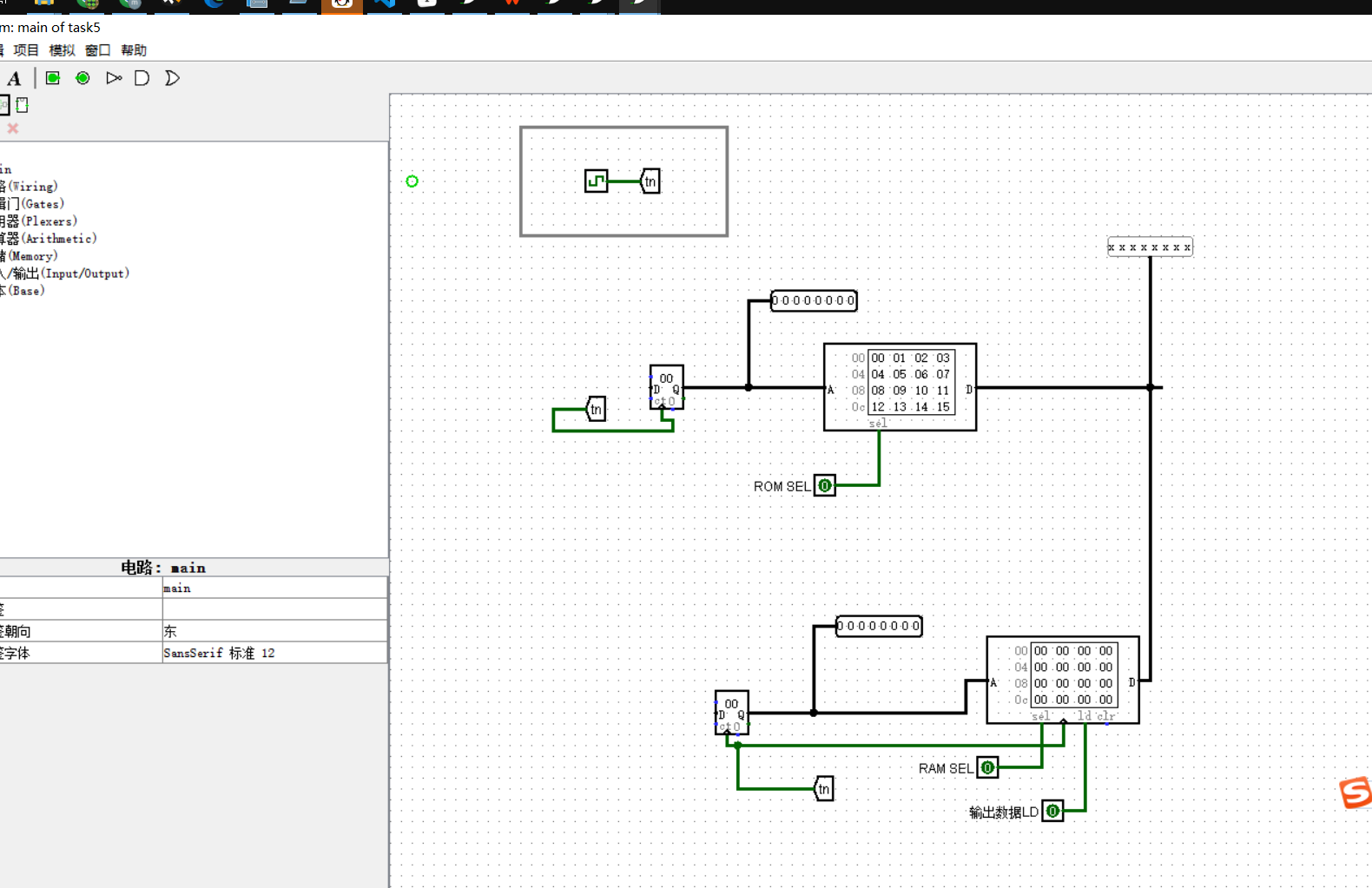

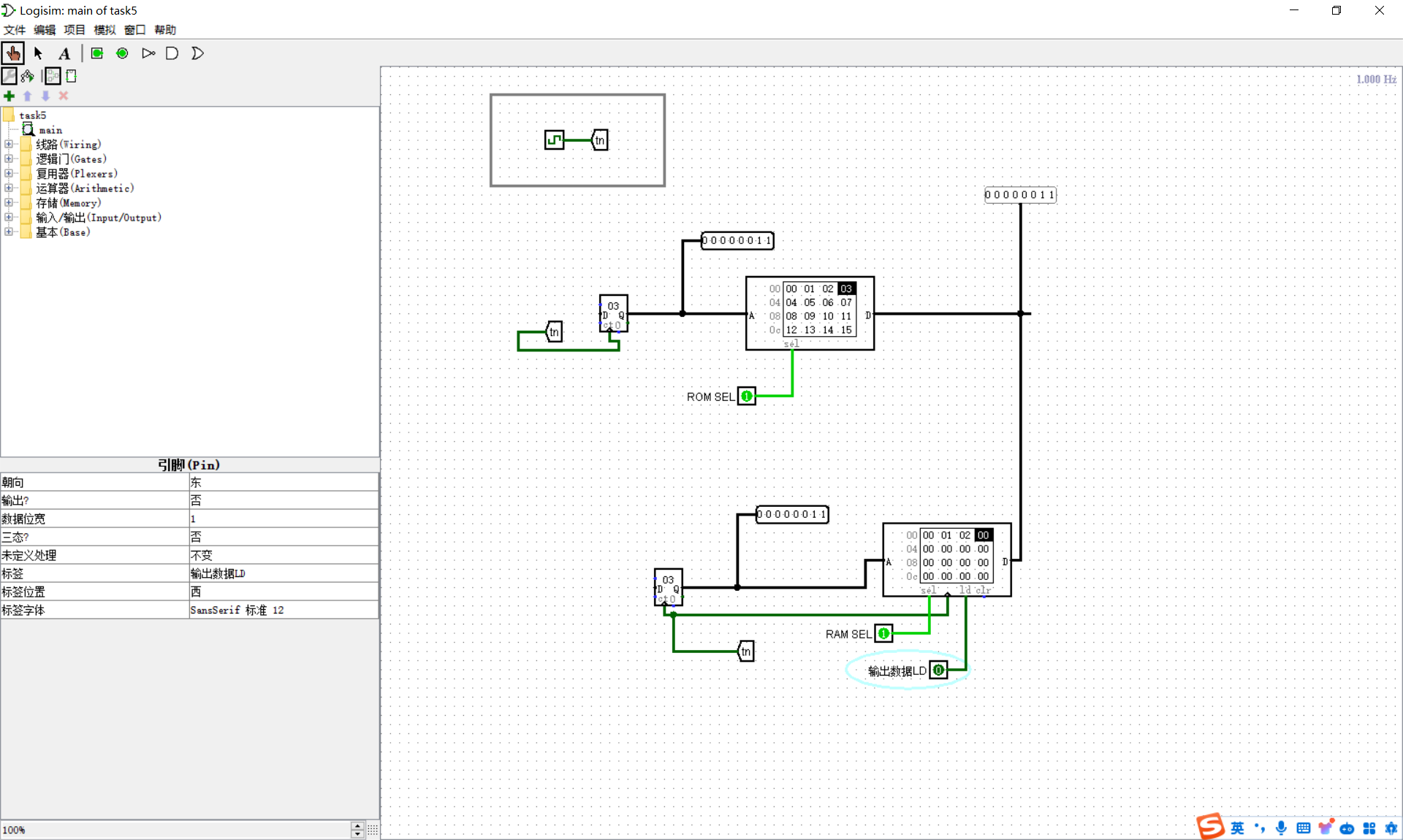

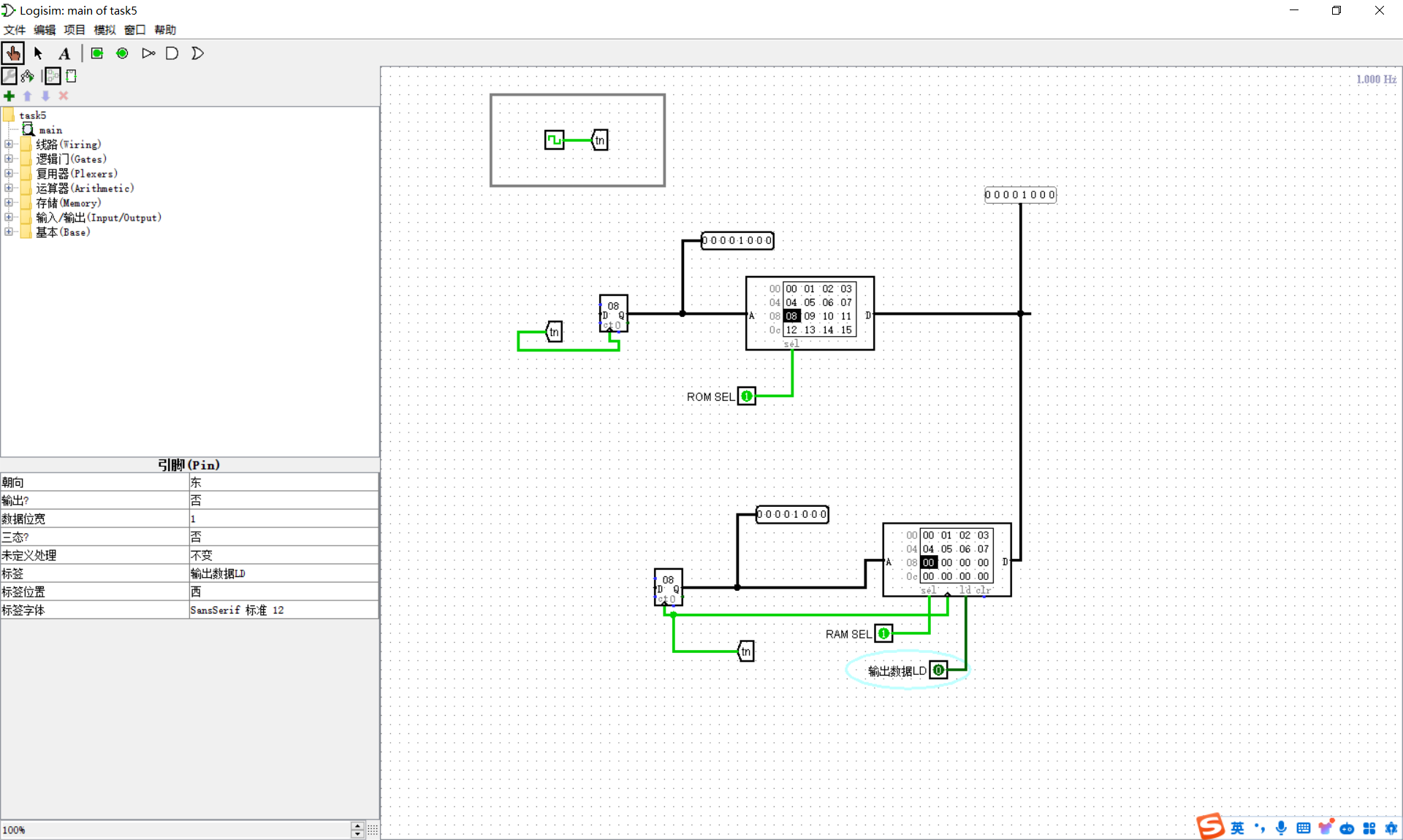

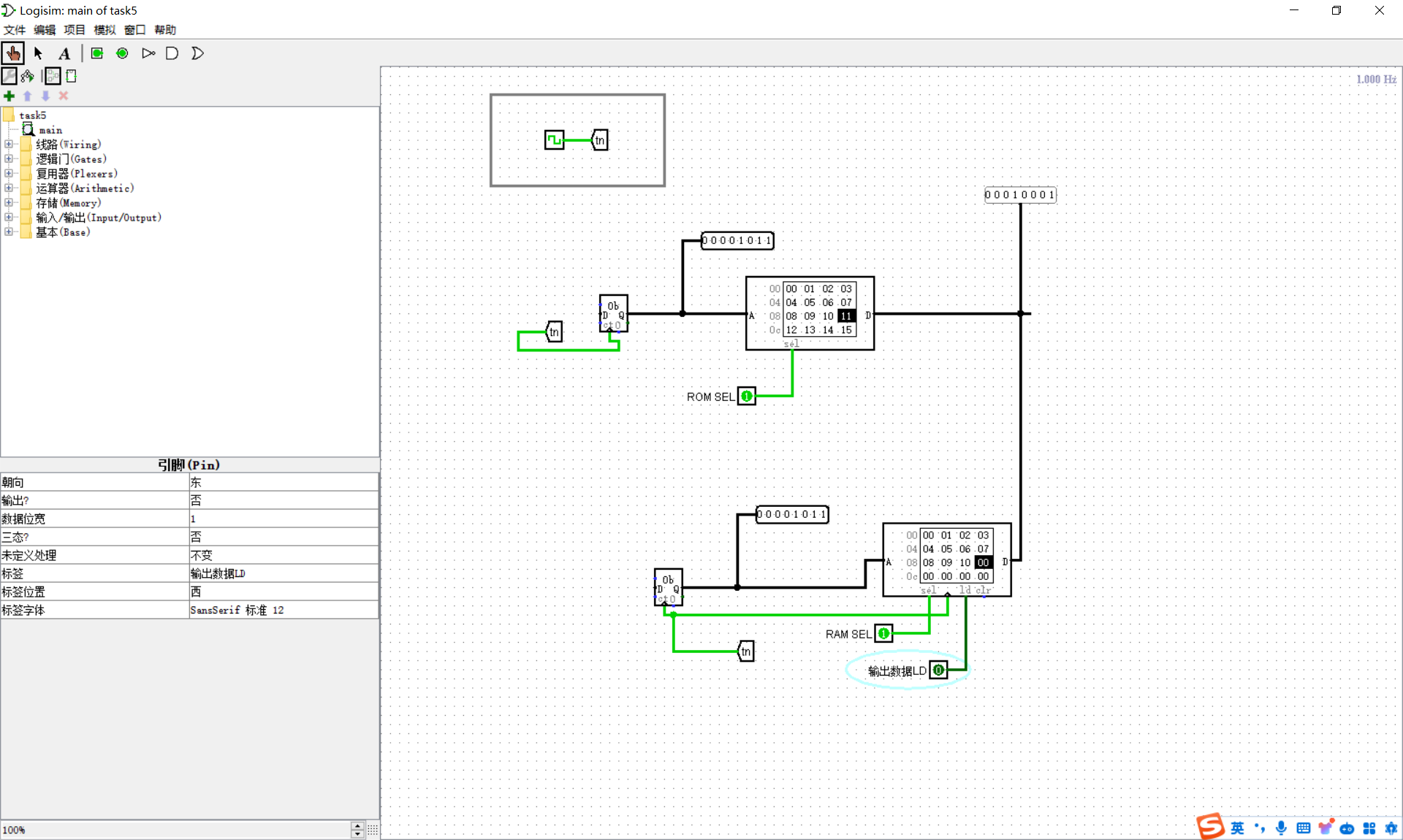

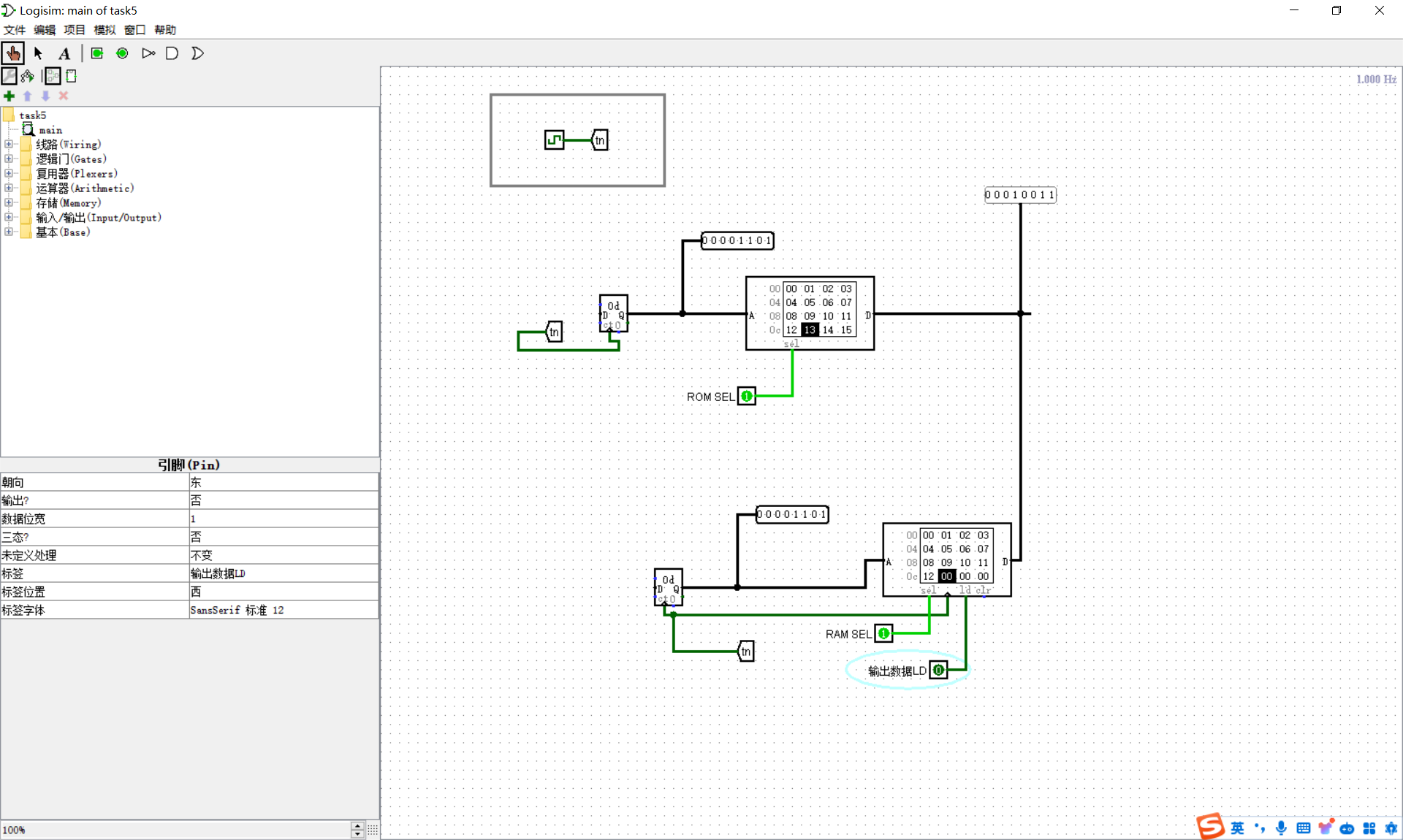

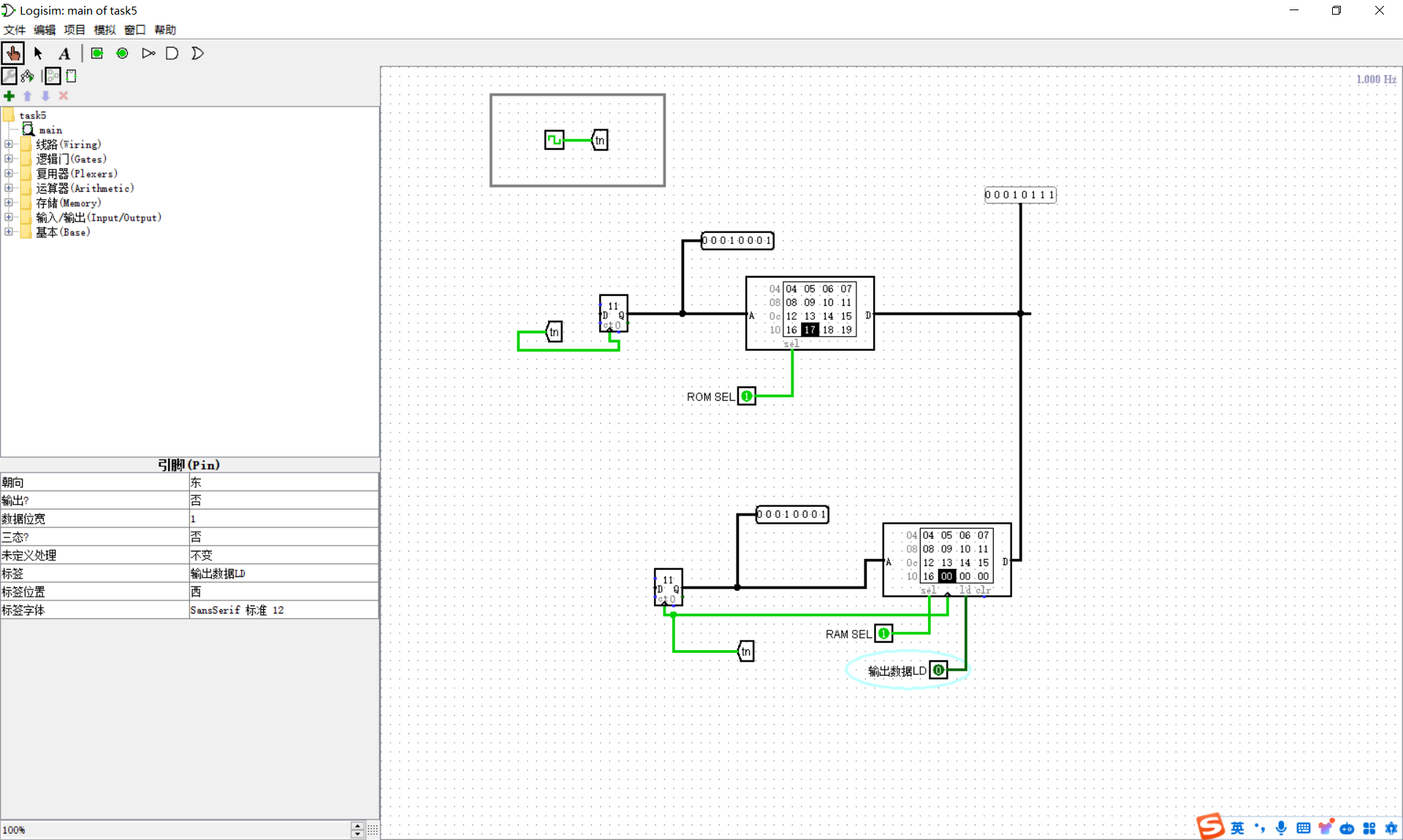

任务5:RAM写入实验

RAM写入实验 在logisim的管理窗口创建如下子电路,完成下图的绘制,利用启用时钟模拟在RAM中的所有单元写入数据。

- 打开Logisim并创建一个新的电路。

- 添加一个RAM组件,并设置其大小和地址范围。

- 添加一个地址输入端口和一个数据输入端口,以便将数据写入RAM。

- 添加一个时钟源(Clock)以便模拟时钟信号。

- 使用时钟模拟将数据写入RAM中的各个单元。

- 添加一个数据输出端口,以显示RAM中的存储数据,并可以更改测试数据。

数据随便弄点

v2.0 raw

0 1 2 3 4 5 6 7

8 9 10 11 12 13 14 15

16 17 18 19 20 21 22

23 24 25 26 27 28这样就可以啦

记得时钟线一定要连好。

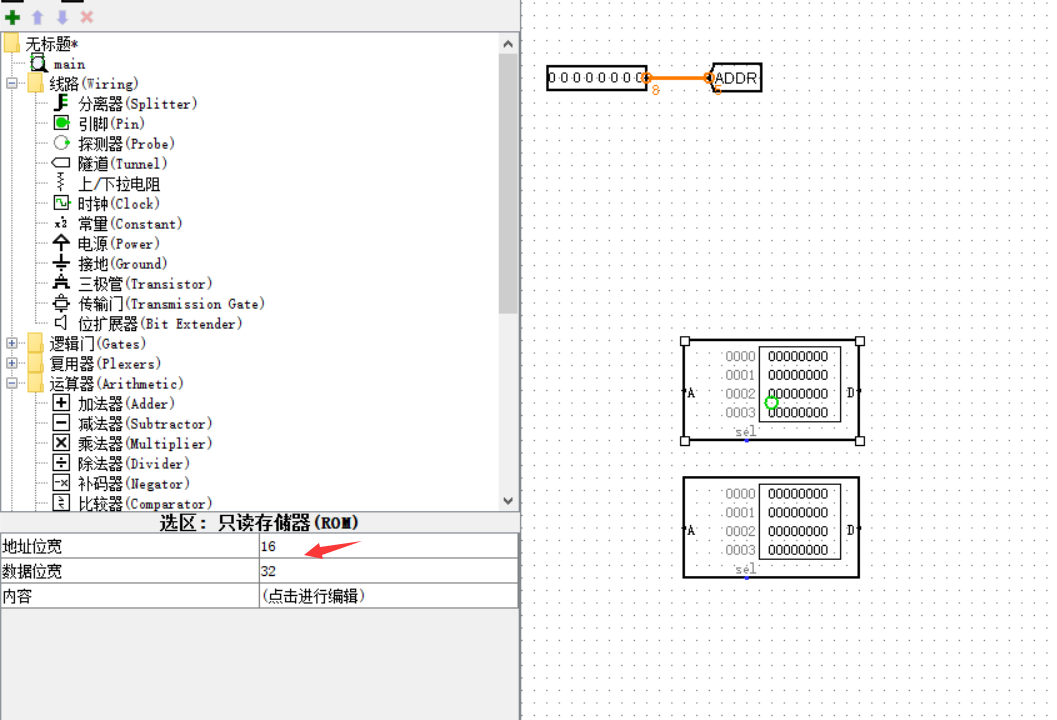

任务6:8*16K 32位存储器电路

做如下8*16K 32位存储器电路(更改存储数据)

- 打开Logisim并创建一个新的电路。

- 添加8个32位存储器芯片,并设置其大小和地址范围,以创建8*16K 32位存储器。

- 添加一个地址输入端口和一个数据输出端口。

- 连接地址输入端口到存储器的地址输入,并将数据输出端口连接到存储器的数据输出。

- 使用Logisim来更改地址总线地址数据,观察输出数据的变化。

16*32的

画完了