计算机组成原理3

https://type.dayiyi.top/index.php/archives/222/

实验过程

1. RS触发器

1.1 介绍

RS触发器是数字电路中的核心元件,经常被用作更复杂触发器的基础。例如,它可以进一步改进为D触发器,以完成更多的任务。RS触发器在数字电路中负责同步和管理电路的工作。

1.2 电路结构与绘制

RS触发器由两个与非门或或非门(如G1和G2)构成,通过交叉连接输入输出端得到。这种交叉连接创建了正反馈,这是所有触发器电路的关键特性。

- 输入:R、S

- 输出:Q、~Q

状态定义如下:

- 0态:Q=0,~Q=1

- 1态:Q=1,~Q=0

1.3 模拟分析

- 当使用或非门作RS触发器时,如果R、S同时为1,那么Q和~Q输出都会为0。这破坏了互补逻辑关系。若同时撤销(变为0),RS触发器将处于不稳定状态。

- 对于与非门组成的RS触发器,当R、S都为0时,Q和~Q都为1,这也破坏了互补逻辑关系。同样,如果它们同时变为1,触发器将不稳定。

1.4 真值表

| R | S | Q | ~Q | 描述 |

|---|---|---|---|---|

| 0 | 0 | 不变 | 不变 | 保持状态 |

| 0 | 1 | 1 | 0 | 置1 |

| 1 | 0 | 0 | 1 | 置0 |

| 1 | 1 | 不确定 | 不确定 | 不稳定状态 |

- 当R=0,S=0时,输出Q和~Q不会发生改变,保持当前状态。

- 当R=0,S=1时,Q输出为1,而~Q输出为0。这称为"Set"或置1操作。

- 当R=1,S=0时,Q输出为0,而~Q输出为1。这称为"Reset"或置0操作。

- 当R=1,S=1时,这是一个禁止的输入组合,因为它导致输出进入一个不确定或不稳定的状态。在实际电路中,这种组合通常避免使用。

1.5 触发器

2. D触发器

2.1 介绍

D触发器是一个记忆元件,有两个稳定状态,常用作时序电路的基础。它在数字逻辑电路中是非常重要的。它可以根据电平触发或边沿触发来工作。电平触发时,当CP(时钟脉冲)为1时触发。而边沿触发则在CP的前沿(从0变为1)进行。D触发器可以置0或置1,当CP=0时,输入信号不会有任何效果,它的状态保持不变,因此也被称为D锁存器。

2.2 真值表

| CP | D | Q_next | 描述 |

|---|---|---|---|

| 0 | x | 不变 | 保持状态 |

| 1 | 0 | 0 | 传输0到Q |

| 1 | 1 | 1 | 传输1到Q |

- 当CP(时钟脉冲)为0时,无论D(数据输入)是什么值,Q的输出都不会改变,因此它被称为"保持"或"锁存"状态。

- 当CP为1时,D的值被传输或复制到Q输出。因此,如果D=0,Q将输出0,如果D=1,Q将输出1。

2.3 触发器

自带的触发器

3. 制作4位寄存器

3.1 电路设计:

- 准备4个D触发器。

- 为每个D触发器设置一个并行输入(D0,D1,D2,D3)和一个并行输出(Q0,Q1,Q2,Q3)。

- 所有的D触发器应共用同一个时钟信号CP。

- 当CP有一个上升沿时,每个D触发器的输入值都会被“锁存”或传输到其对应的Q输出。

3.2 画图

3.3 模拟运行:

- 设置输入D0-D3。

- 触发时钟信号。

正常啦

4. 在Logisim中完成8位寄存器

4.1电路设计:

- 在Logisim中打开一个新的工作区。

- 添加8个D触发器。

- 为每个D触发器设置一个并行输入(D0-D7)和一个并行输出(Q0-Q7)。

- 所有的D触发器都应该连接到同一个时钟信号。

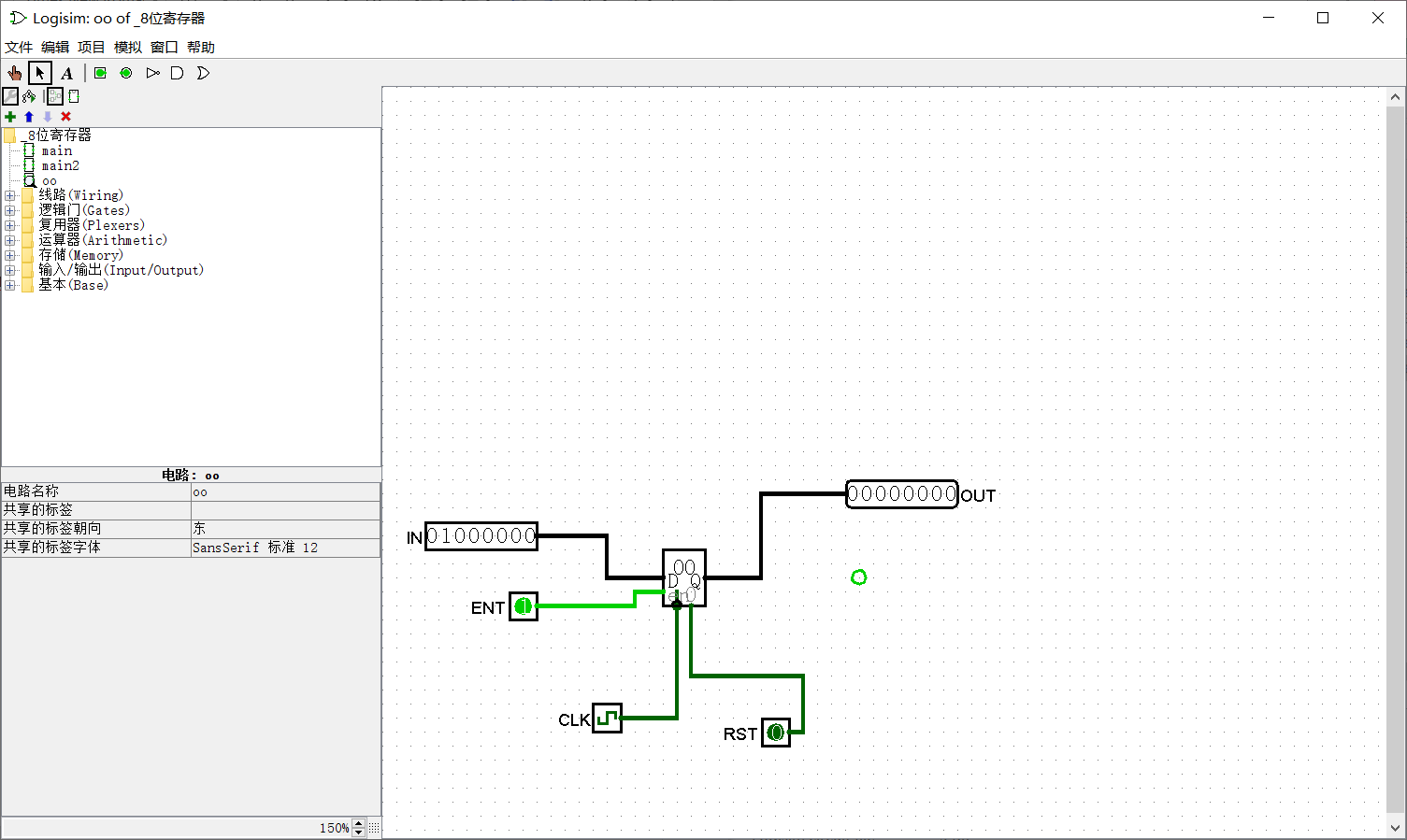

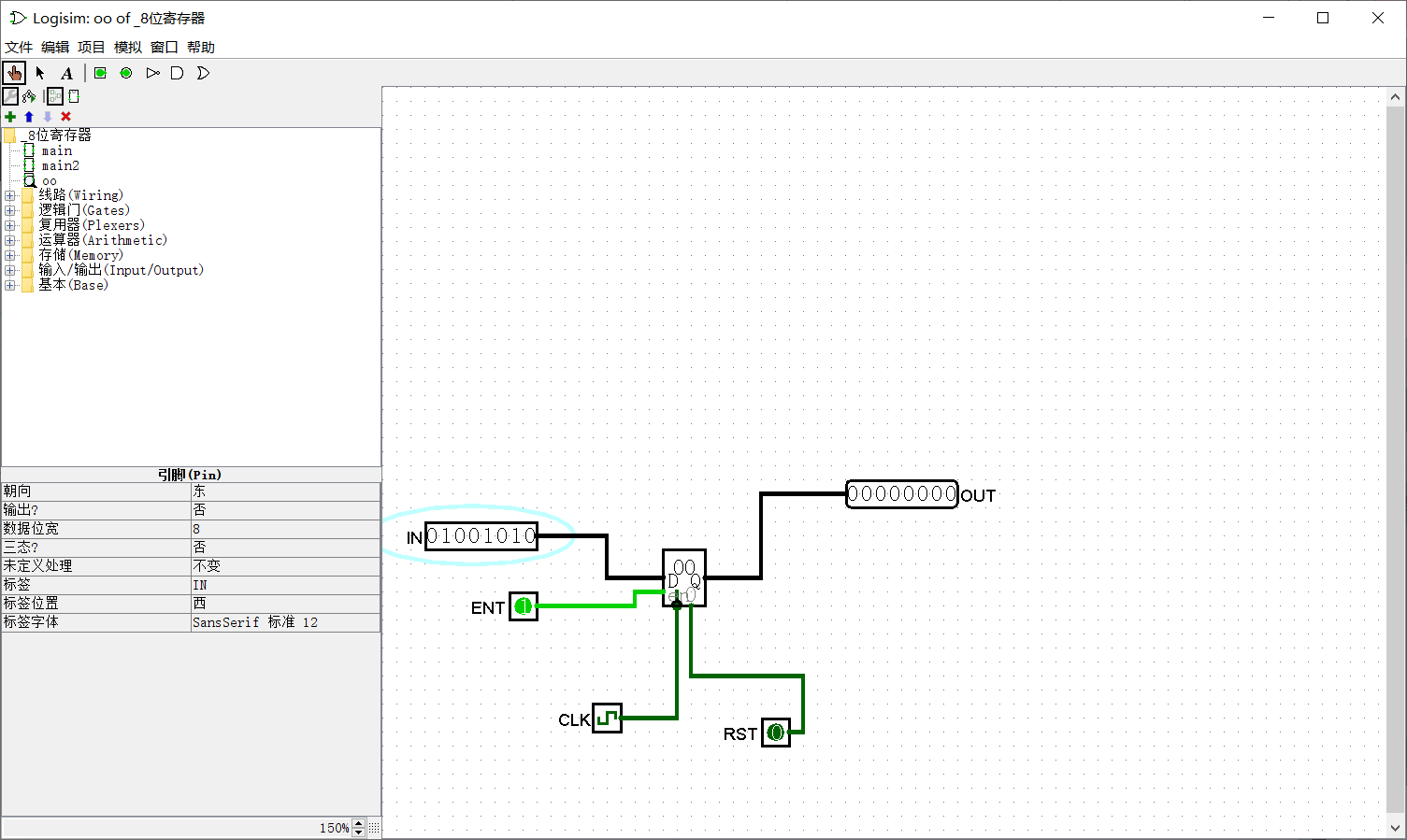

4.2 画图

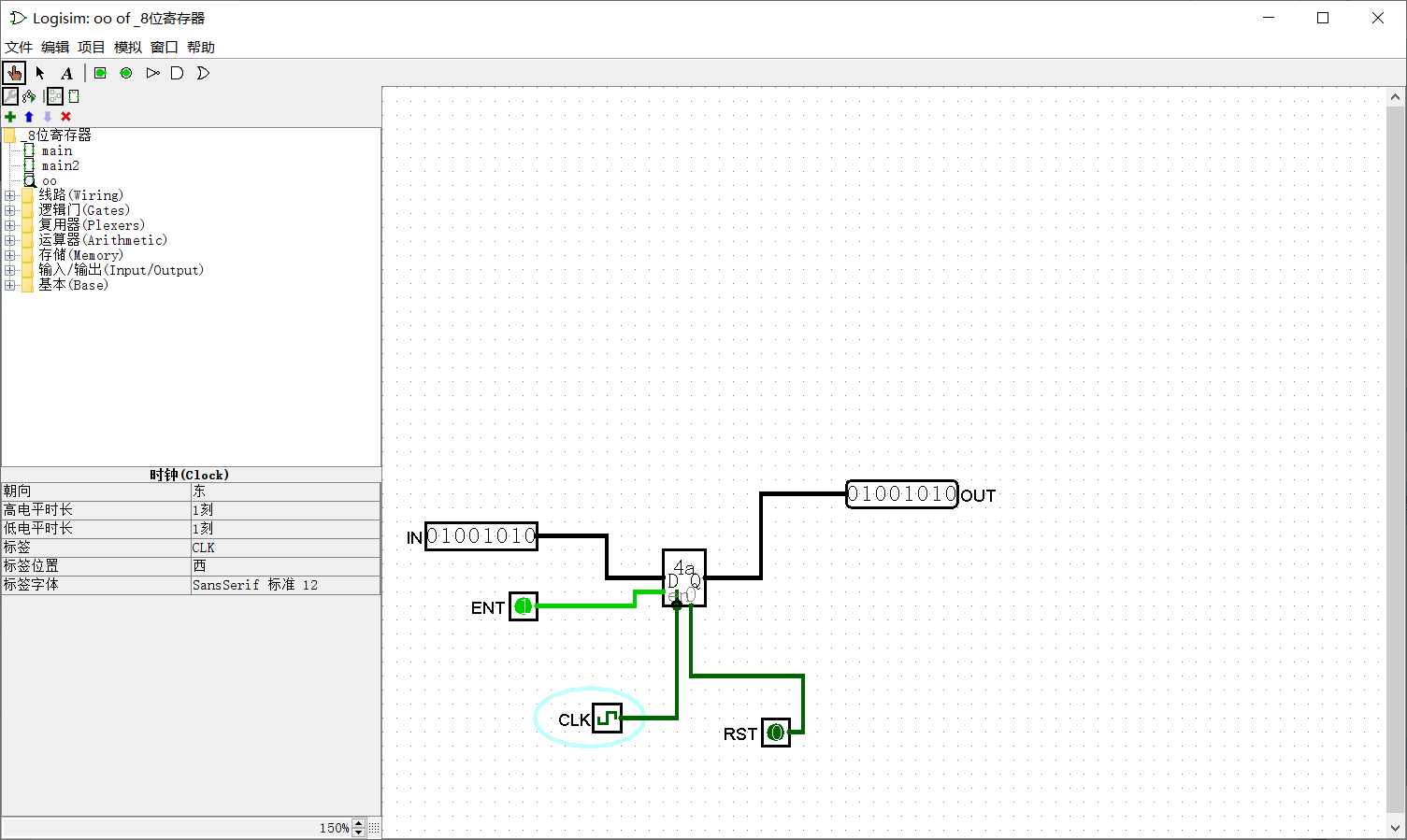

4.3模拟运行:

- 使用Logisim的工具更改D输入的值。

- 激活时钟信号。

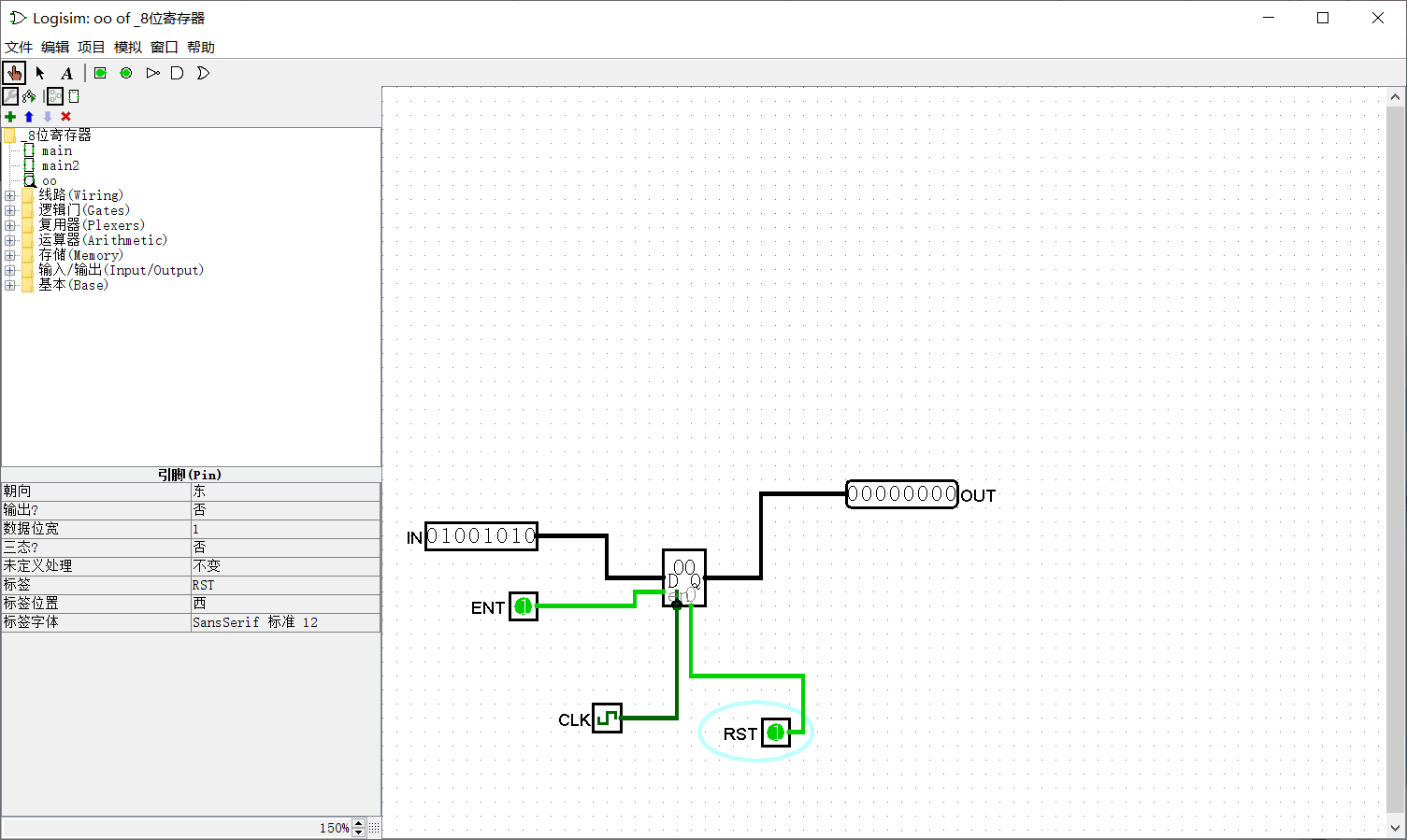

- 测试

RST:

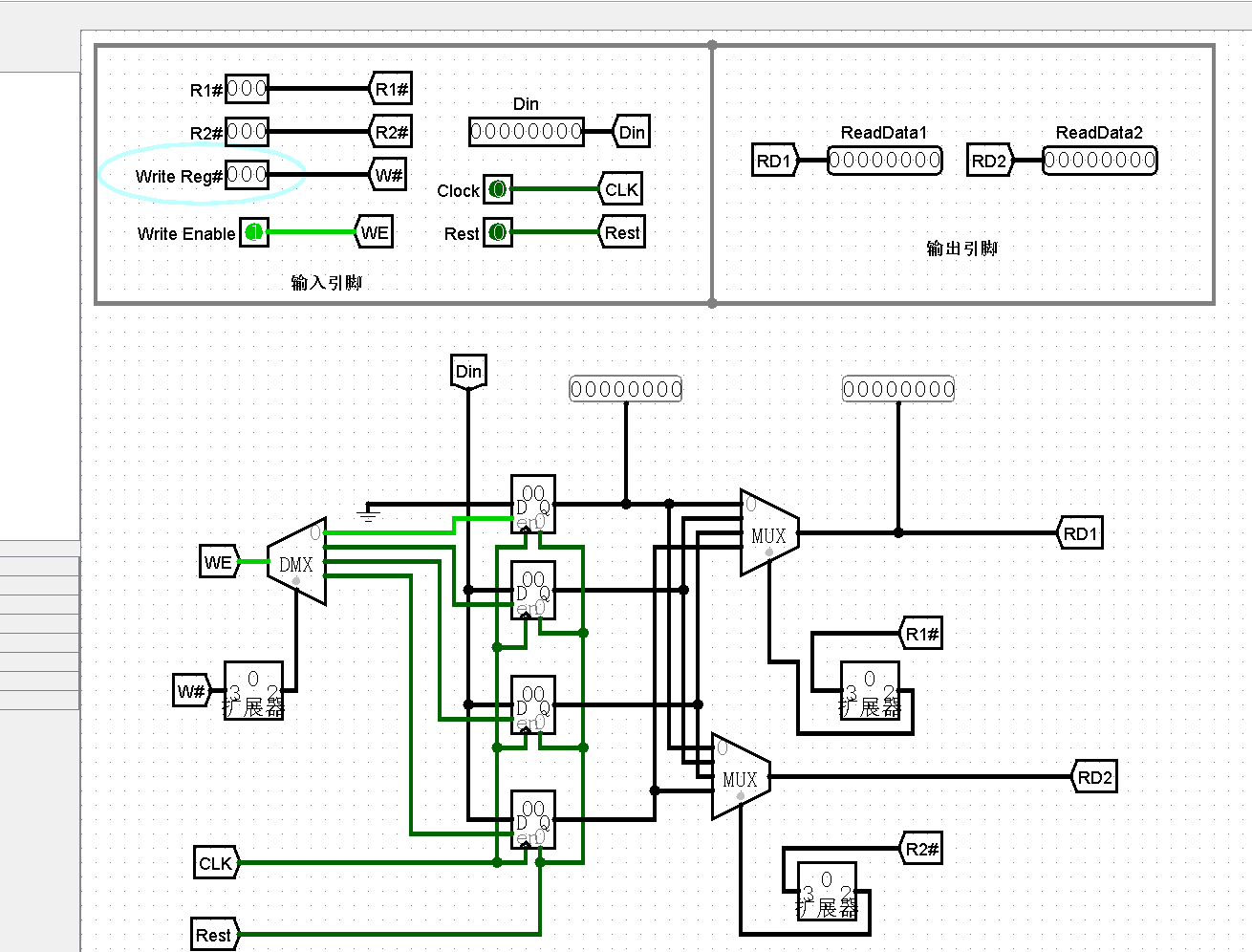

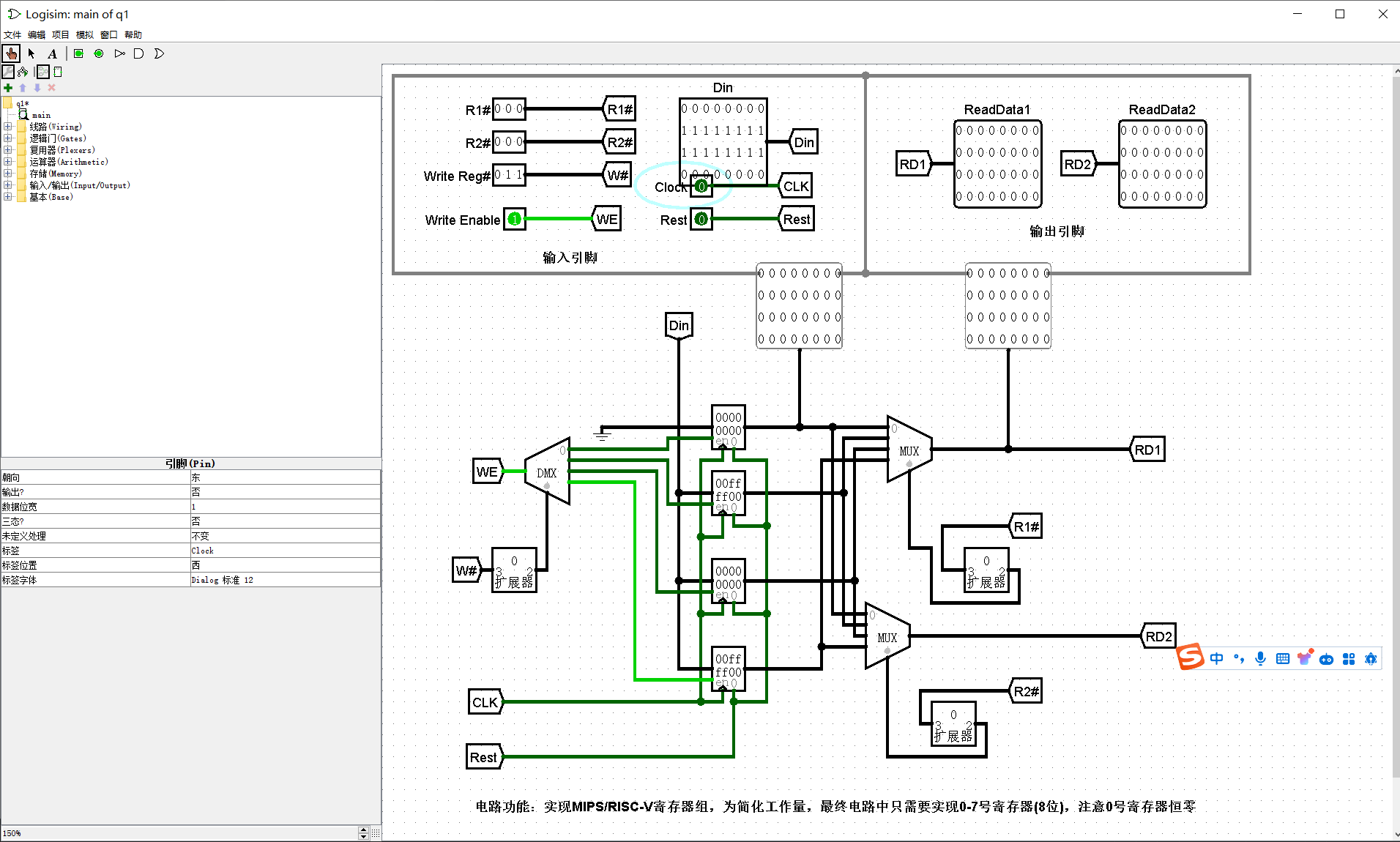

5.利用组件构建 MIPS 8位寄存器设计如下(简化只设计0-1号寄存器)

隧道标记:R1# 为RD1输出选择端 RD1数据输出端1

R2# 为RD2输出选择端 RD2数据输出端2

WE为写使能

CLK为时钟输入 Din为数据输入端

MIPS(Microprocessor without Interlocked Pipeline Stages)是一个RISC(Reduced Instruction Set Computer)架构的微处理器系列。RISC是一种设计思路,它通过减少每条指令所做的工作和简化指令集来提高性能。MIPS架构在过去的几十年中已被广泛应用于许多应用程序,从桌面计算机到嵌入式系统。

MIPS寄存器是存储数据的基本单位,对数据的读写操作都会经过寄存器。在MIPS架构中,寄存器的读写都是同步的,需要时钟信号。

任务:

1. 当WE=1时,通过多路解复用器选择相应寄存器(相应寄存器使能)

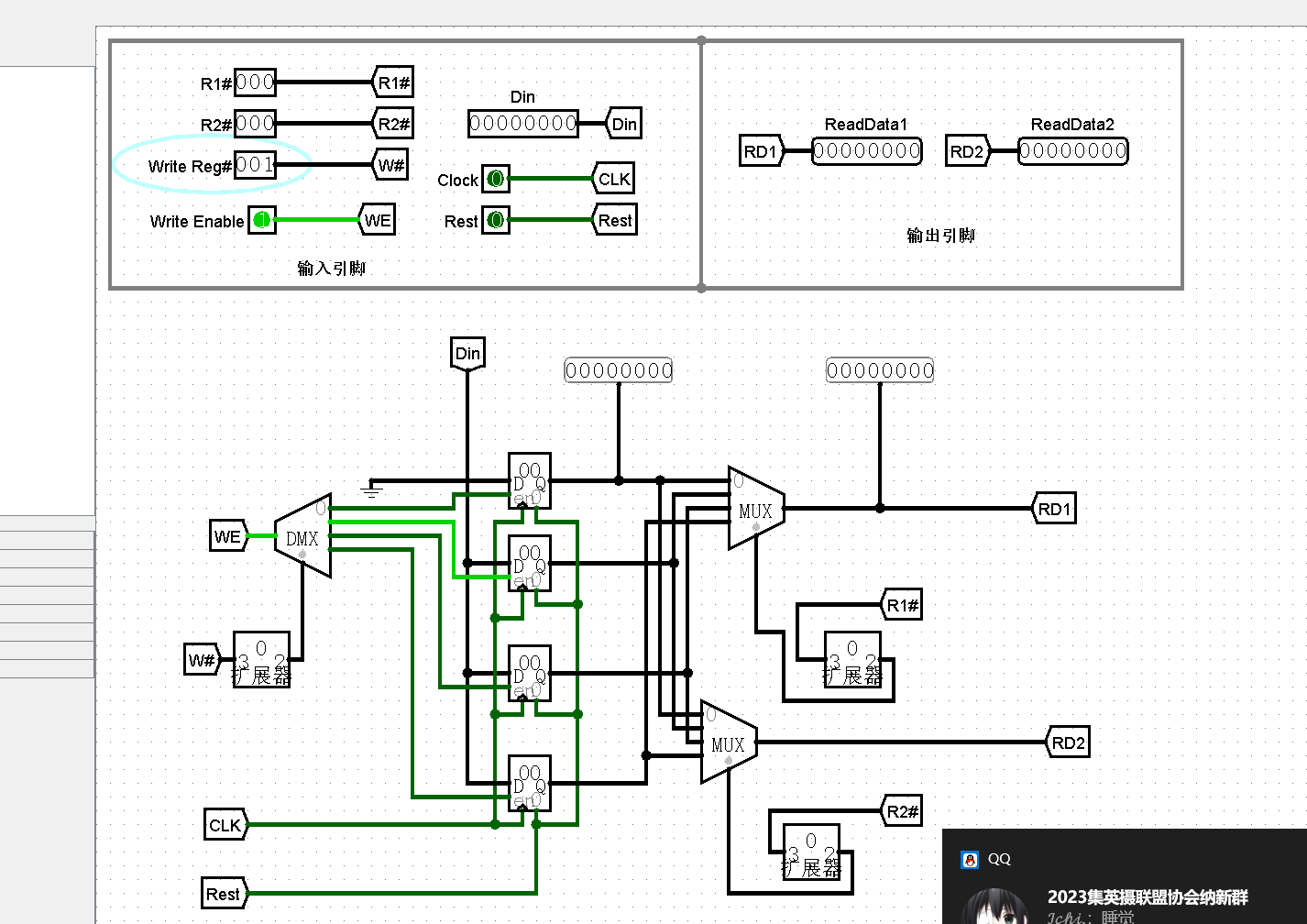

选择0 寄存器:

选择1 寄存器:

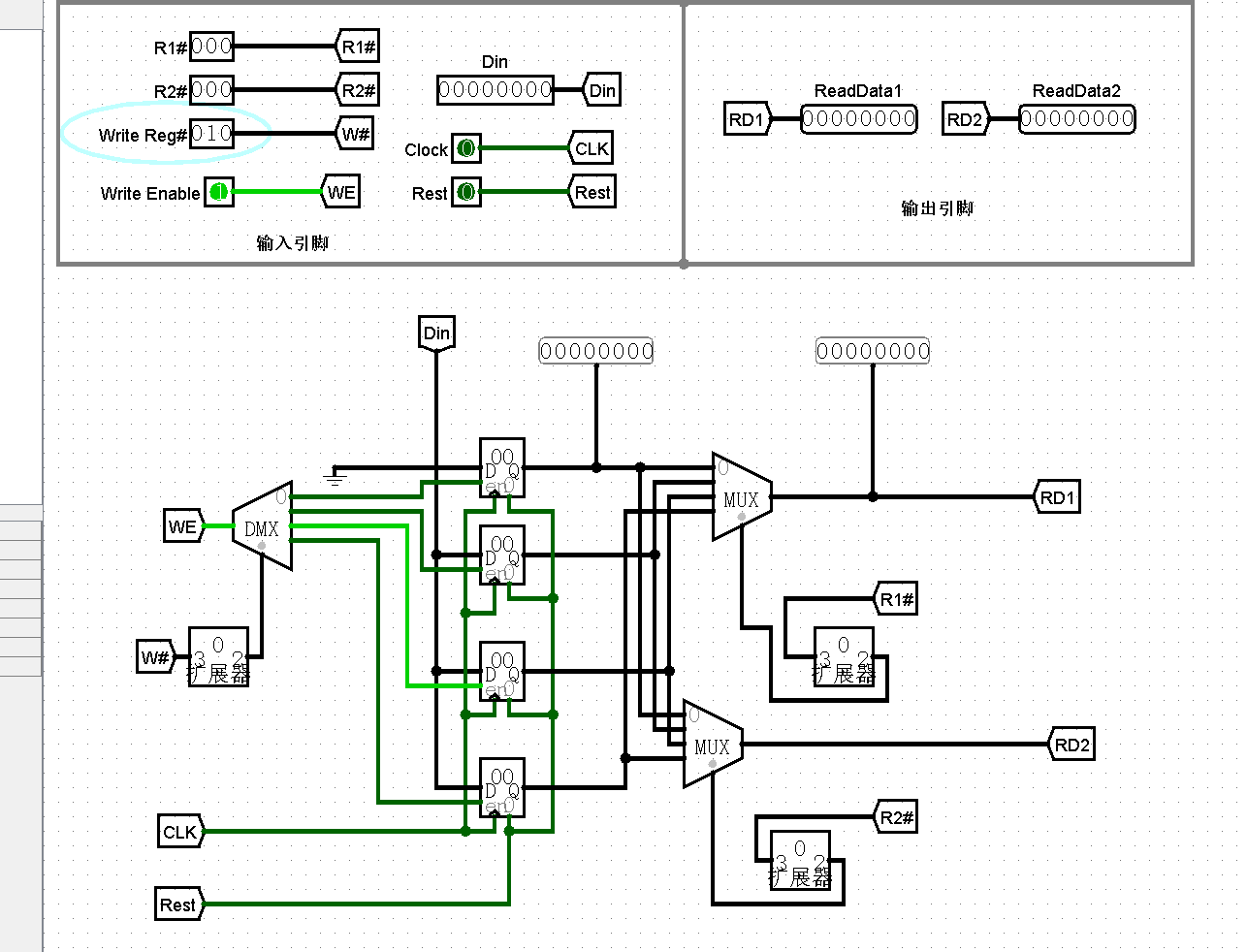

选择2 寄存器:

选择3 寄存器:

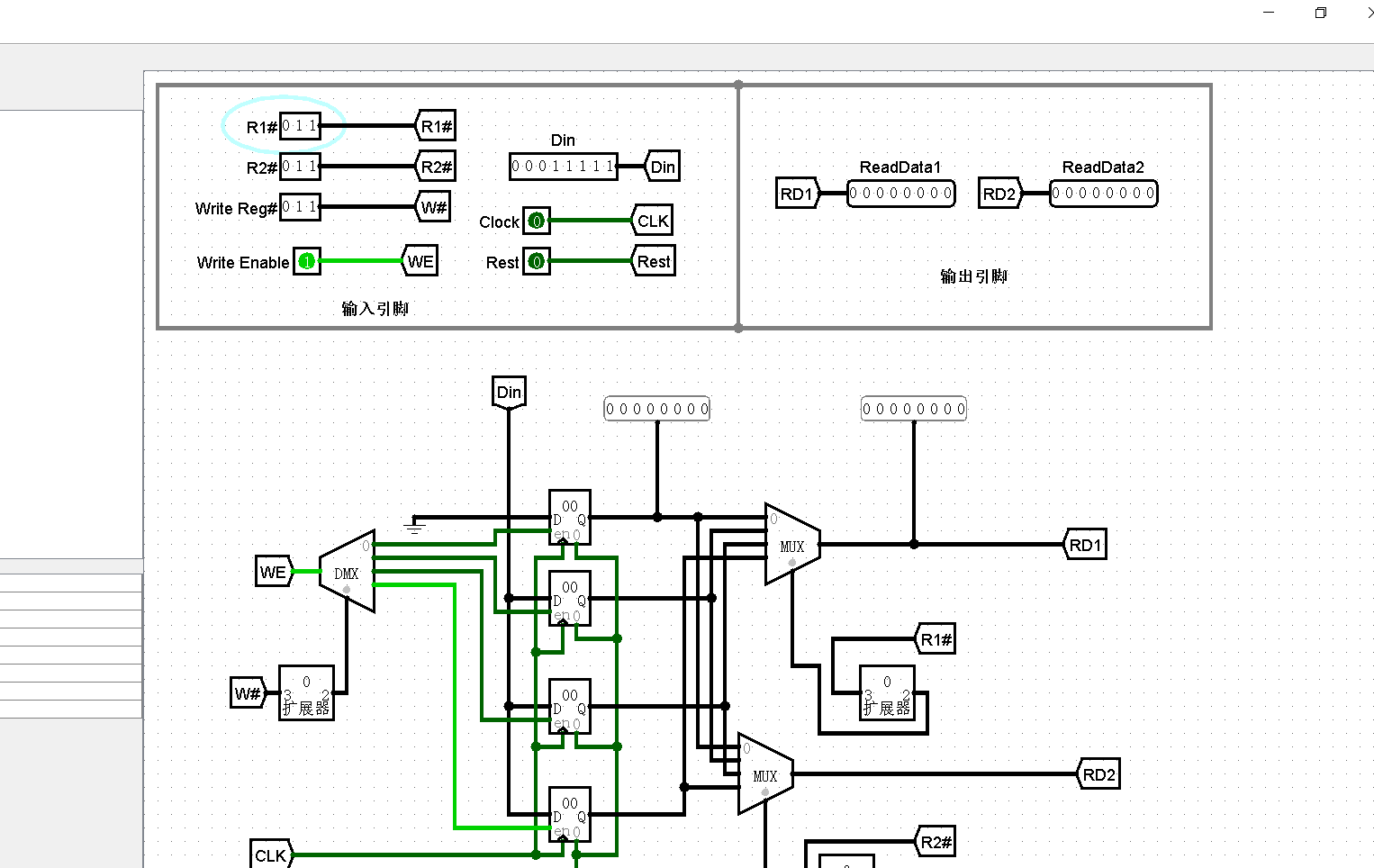

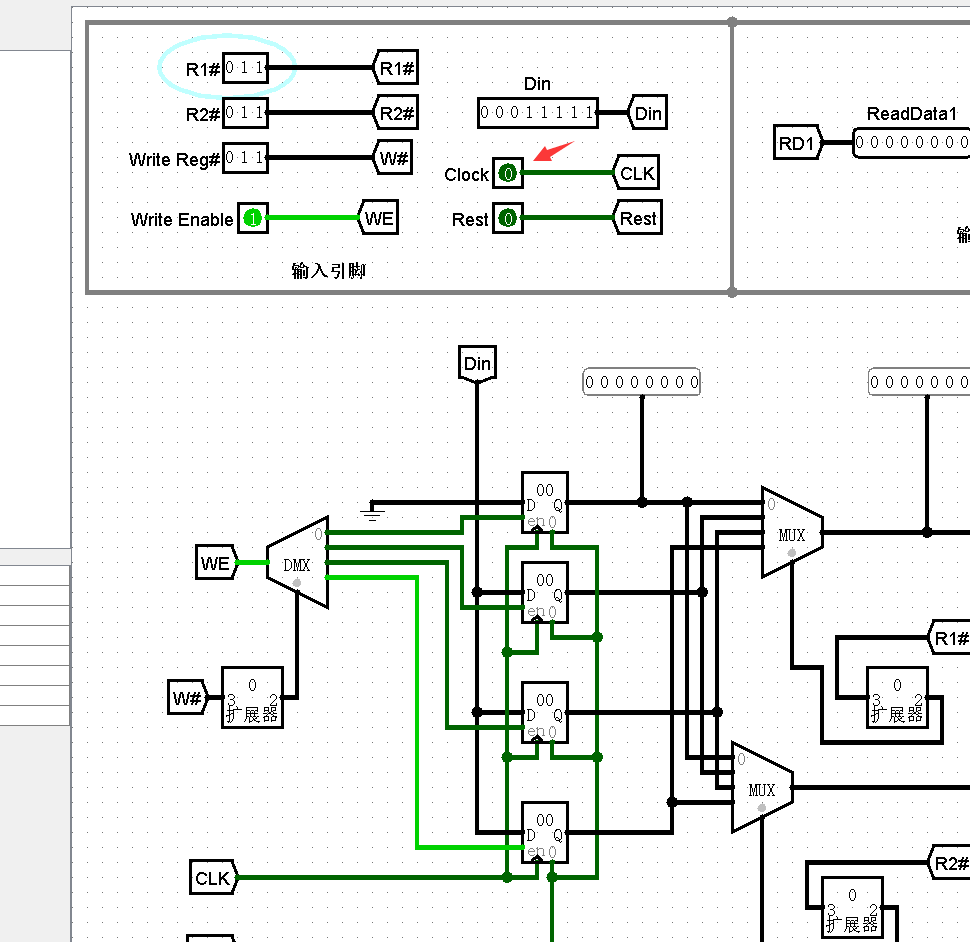

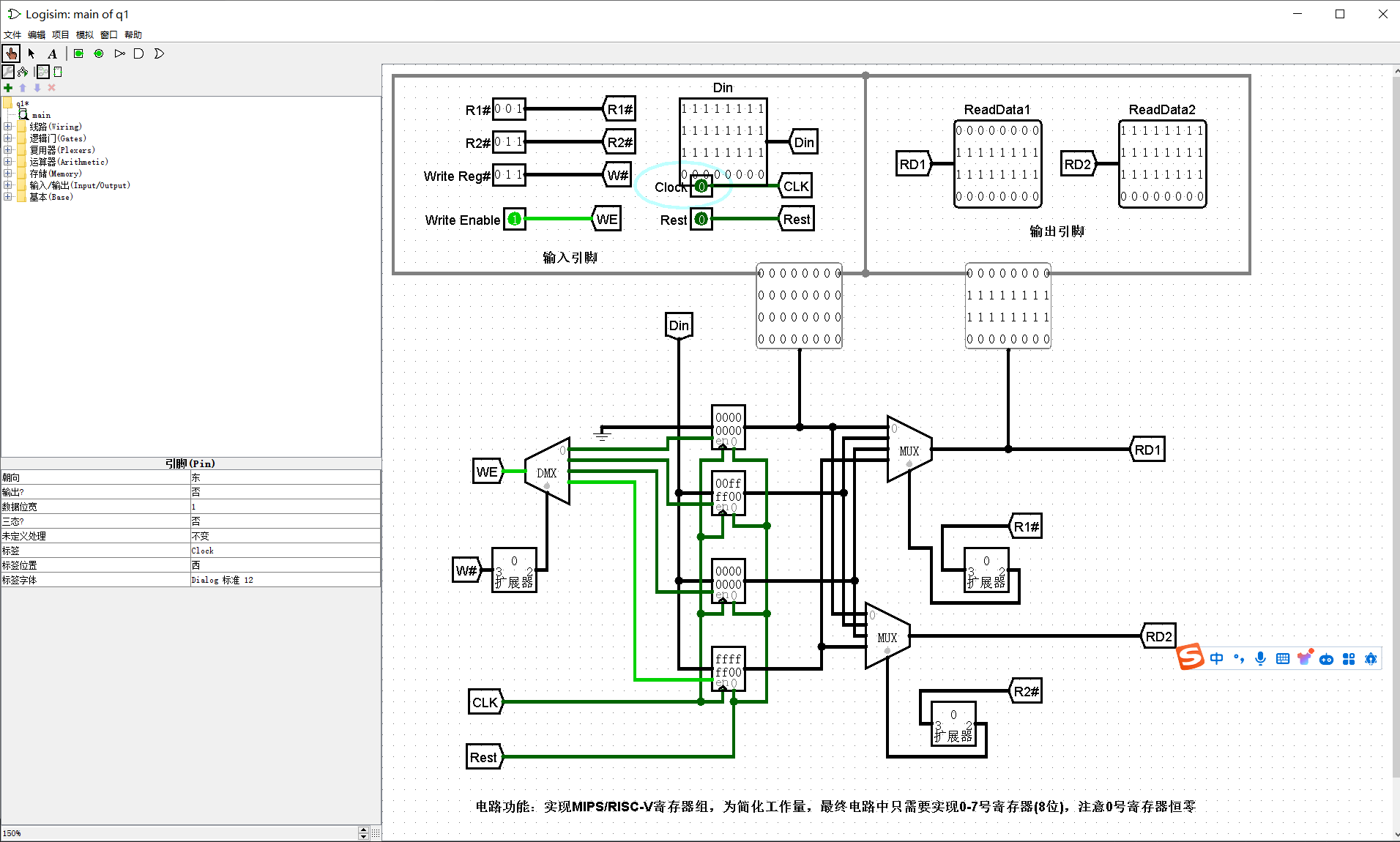

2. 设置DIN数据,R1、R2选择输入端口

设置寄存器选择4寄存器,数据位00011111

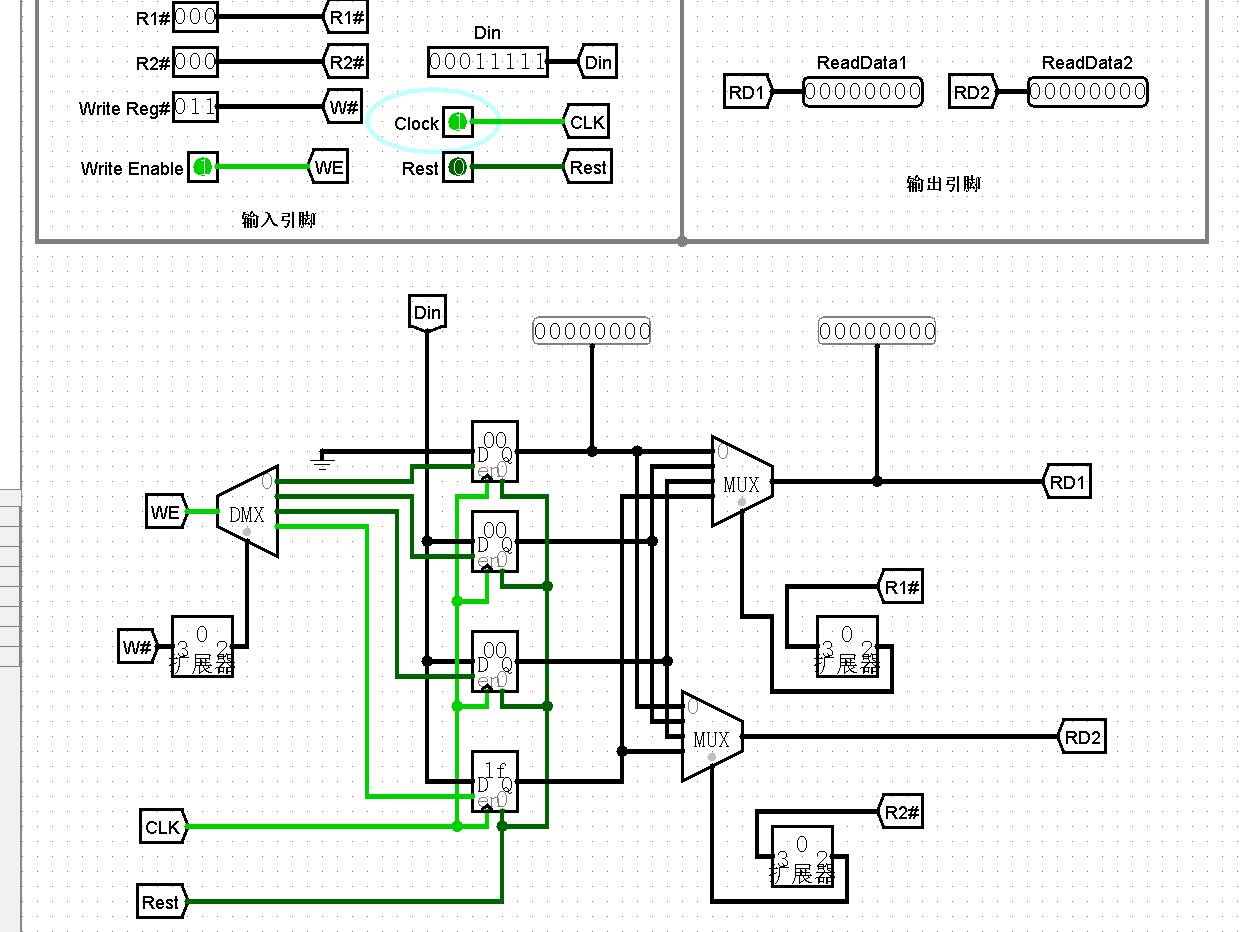

3. 给定CLK时钟(电平0-1) RD1、RD2端输出数据

点击时钟:

写到寄存器4

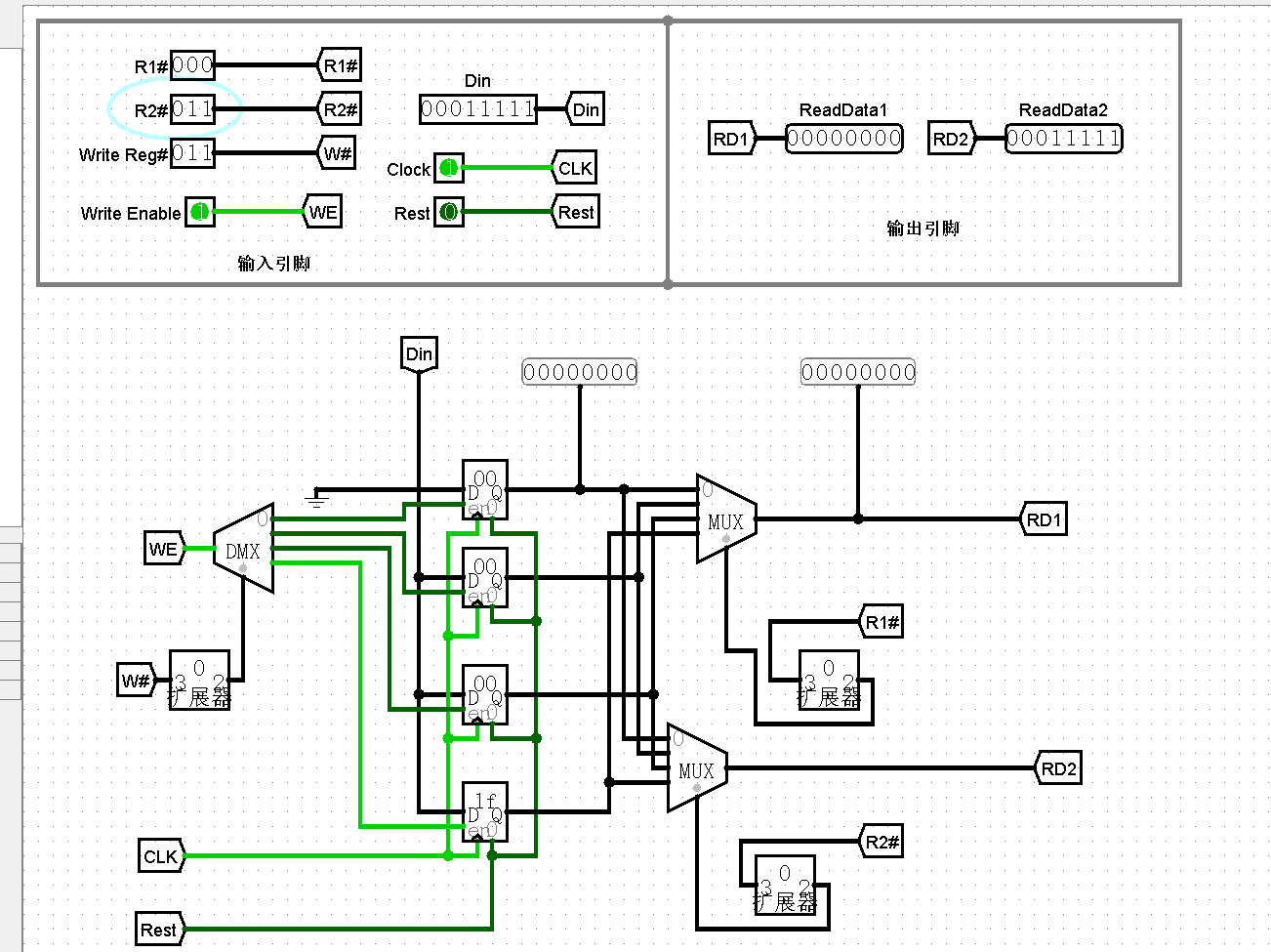

R2读取寄存器4:

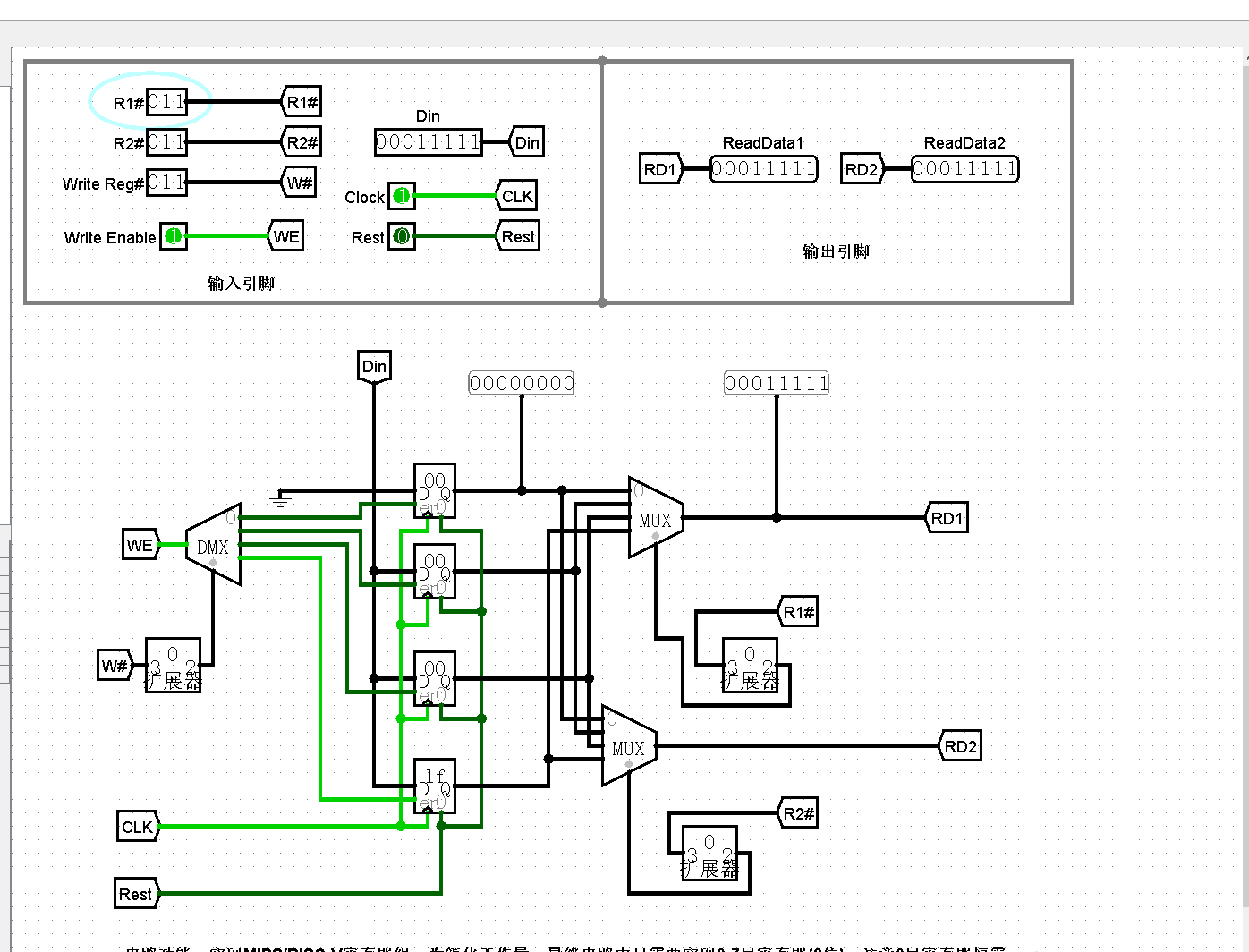

R1 读取寄存器4:

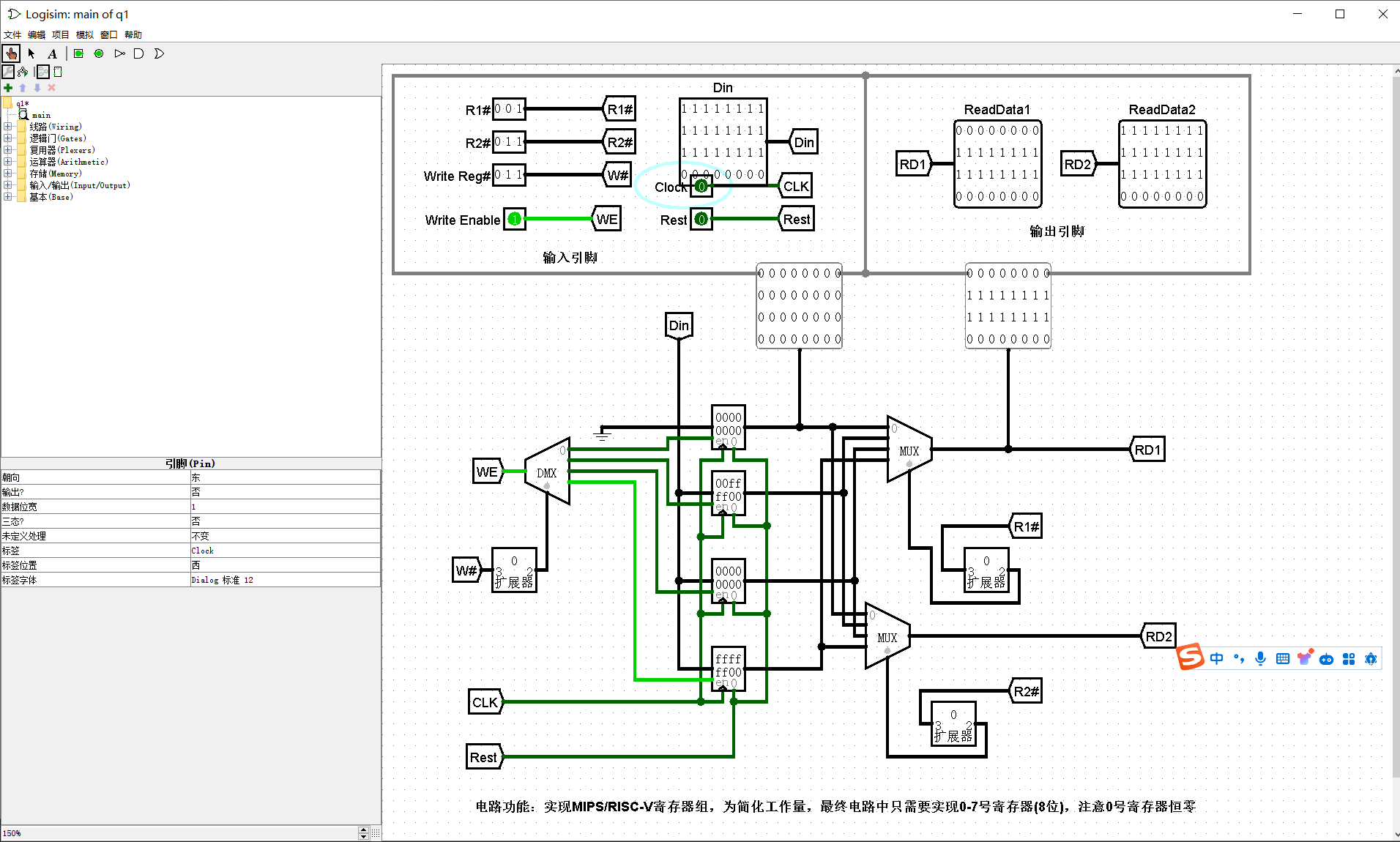

4. 测试寄存器电路以上,并扩展完成8位0-3位寄存器电路,分析并模拟运行电路并测试(结果写入实验报告)

感谢老师的文件,已经扩展完了。

主要的内容就是,解码器多点,然后加上两个

DMX MUX上面的线路上多点点就可以啦。

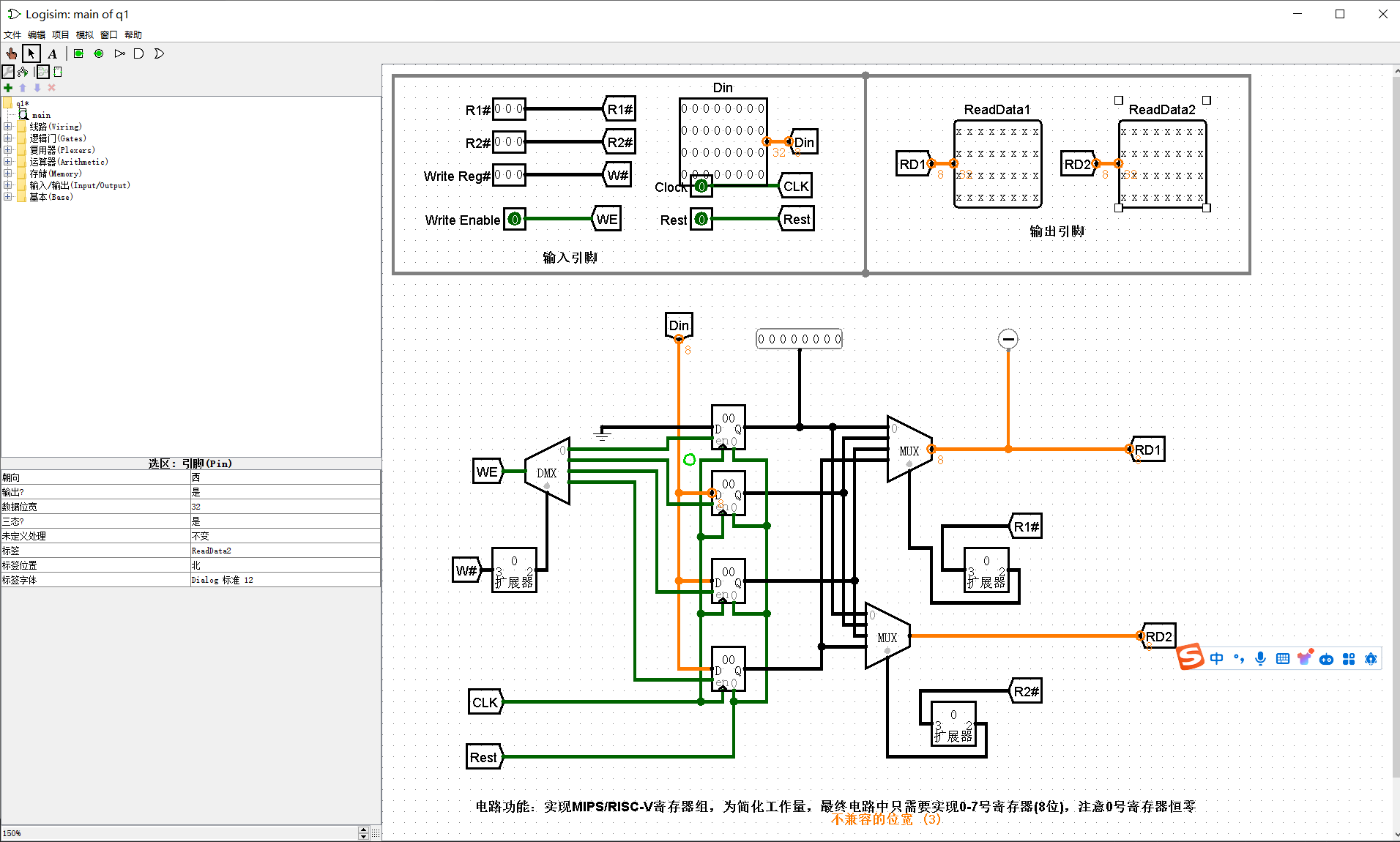

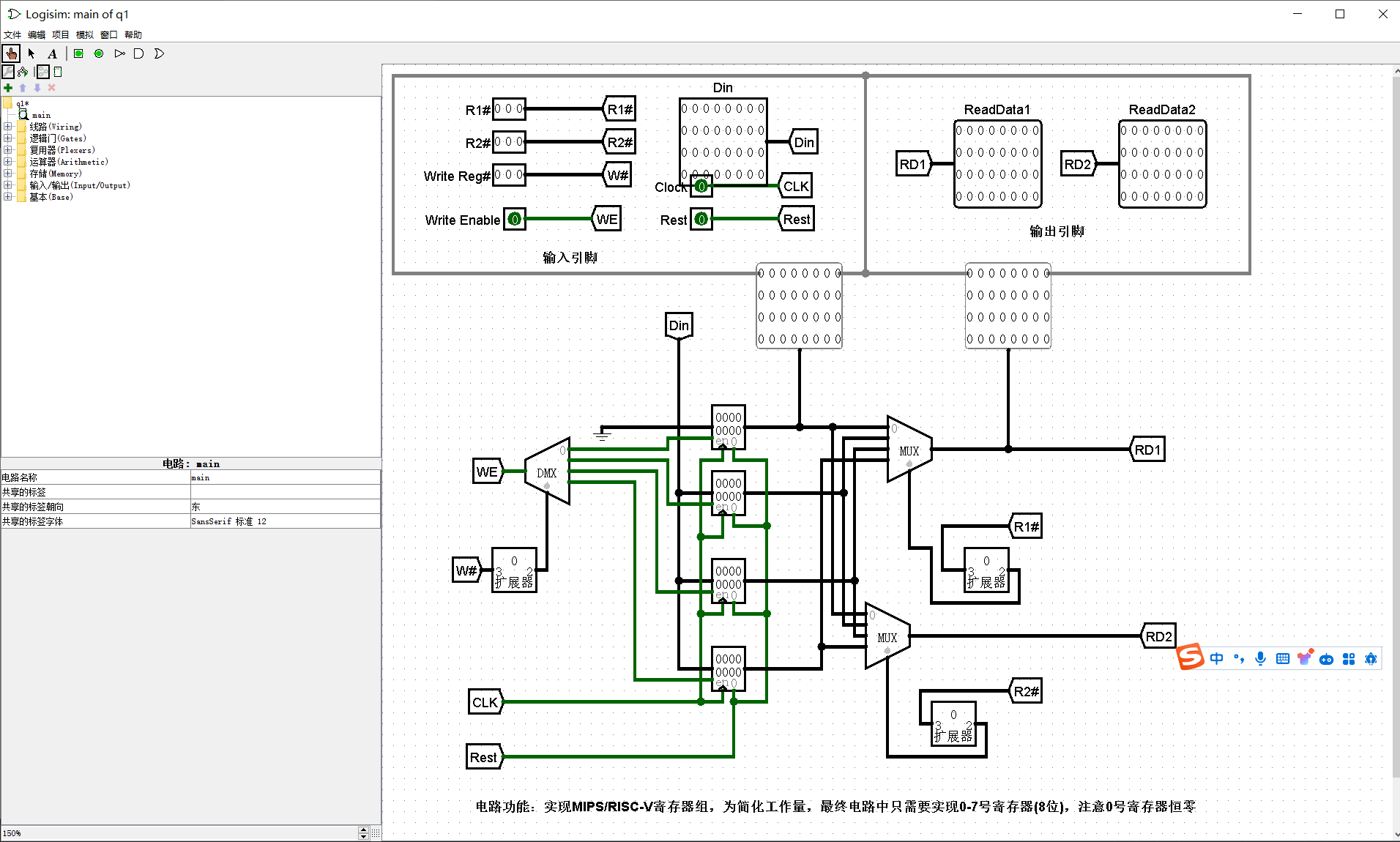

5.根据以上例程利用组件构建 MIPS 32位寄存器设计如下(简化只设计0-3号寄存器)

这里扩展

6.当WE=1时,通过多路解复用器选择相应寄存器(相应寄存器使能)

选择就行了。

这里0 0 0 寄存器(恒为0的寄存器)

0 1 1 寄存器

1 0 2 寄存器

1 1 3 寄存器

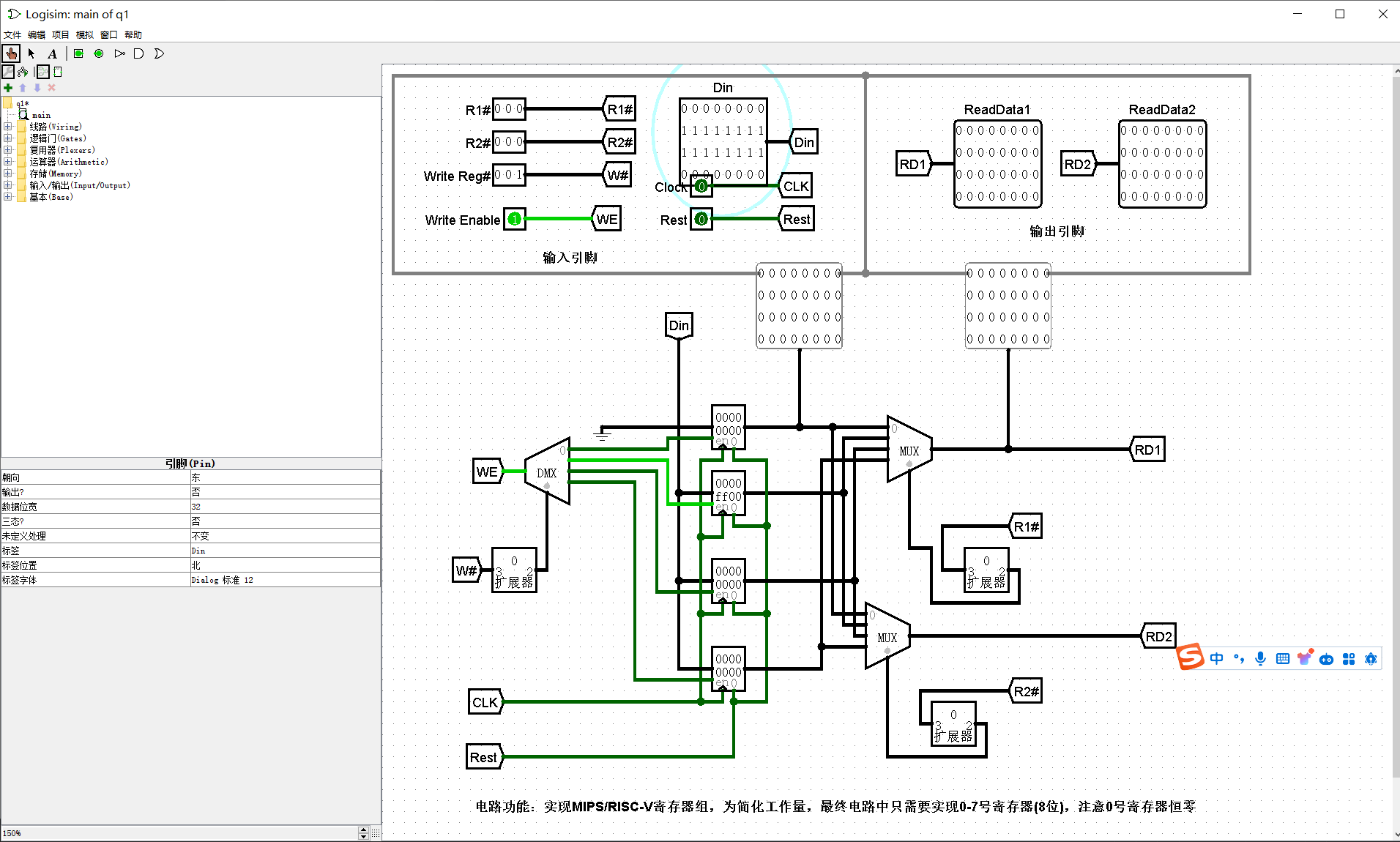

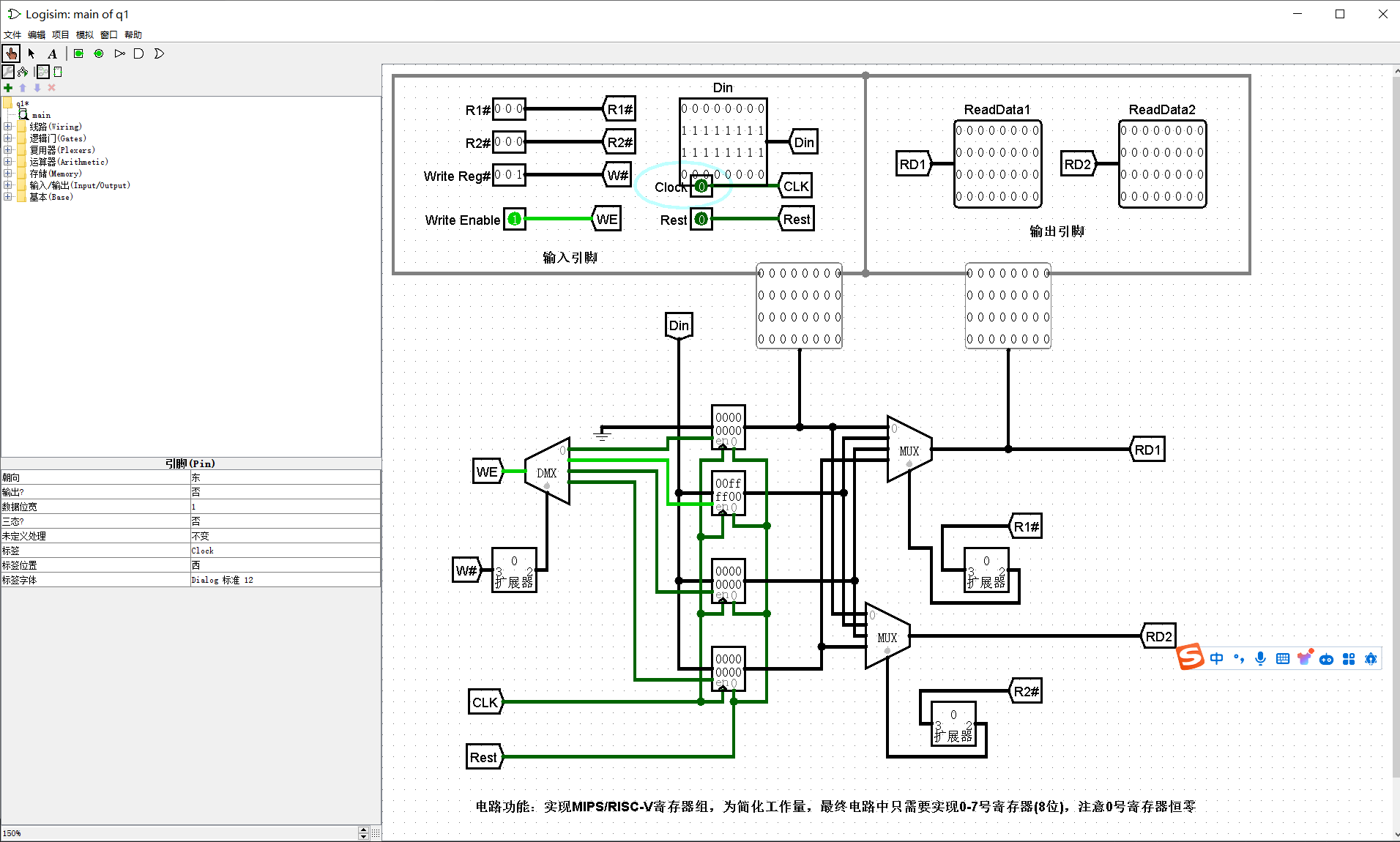

7.设置DIN数据,R1、R2选择输入端口

可以玩玩啦

- 选择输入寄存器(WR)

- WE 启动选择

- Din写入数据

- R1 选择要读的寄存器

- R2 选择要读的寄存器

- 跳时钟

- 就可以显示数据啦。

8. 给定CLK时钟(电平0-1) RD1、RD2端输出数据

done

但那个附录小故事还是挺好看的。