计算机组成原理2

更好的浏览:https://type.dayiyi.top/index.php/archives/219/

1.利用Logisim软件设计一个1位加法器

加法器是数字系统中的基本逻辑器件,减法器和硬件乘法器都可由加法器来构成。

全加器,全加器是实现两个一位二进制数及低位来的进位数相加(即将三个二进制数相加),求得和数及向高位进位的逻辑电路。所以全加器有三个输入端(A,B,C)和两个输出端S,Cout)。

设计思路:一个全加器可以用两个1位半加器和或门组成。

1.1半加器:

真值表

| A | B | Sum (S) | Carry (Cout) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

- 和(Sum,): S=A⊕B。

- 进位(Carry, Cout): C = AB

也可以直接生成

全加器:

输入:A、B、C

输出:S、Cout

同样的,还是先写真值表

| A | B | C | Sum (S) | Carry (Cout) |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

然后直接生成就可以啦

逻辑关系式:

和(Sum, S):S=A⊕B⊕C

进位(Carry, Cout): Cout=AB+BC+AC

结果与加法器一样(这个加法器可以调位宽):

2、利用1位全加器设计4位加法器

改下标签:cin和cout

魔改电路位置,直接画就行:

要命:

正常工作了

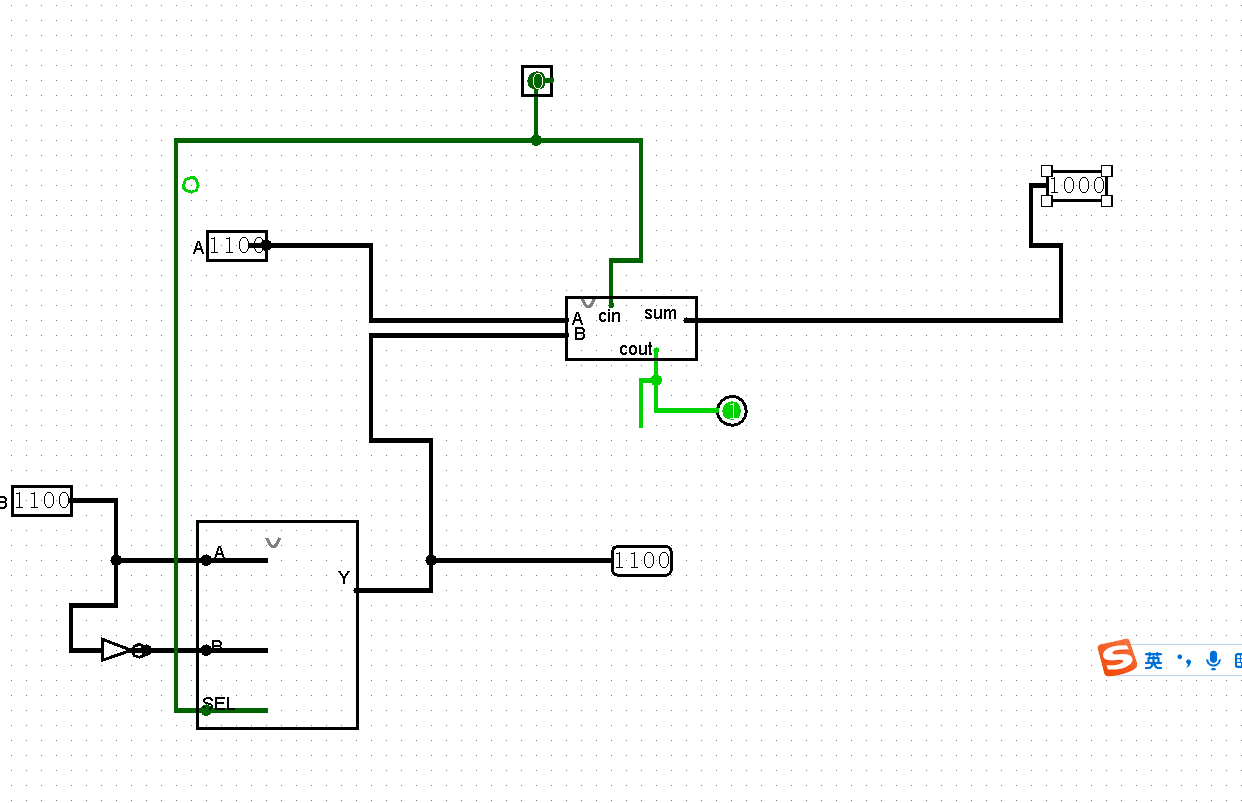

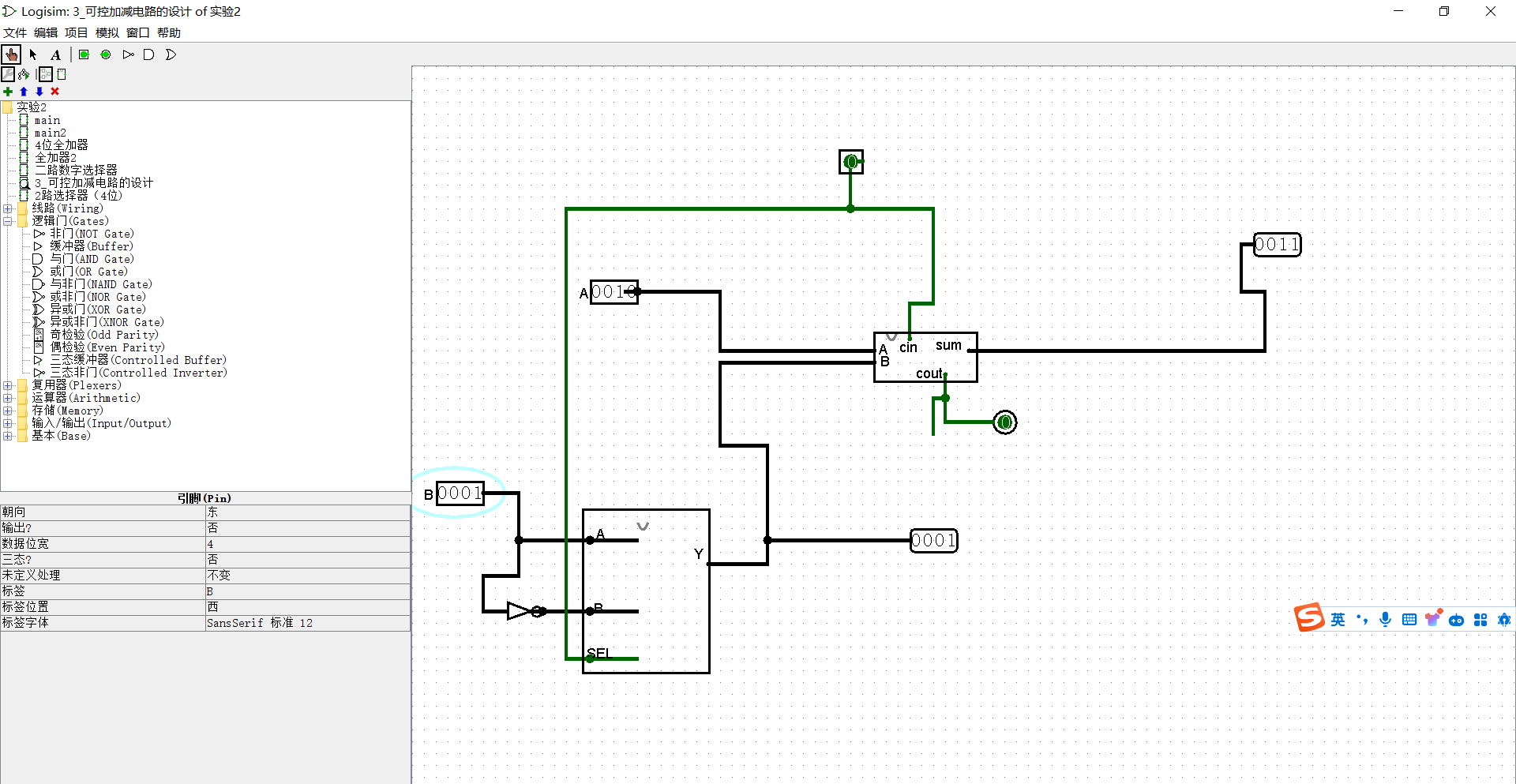

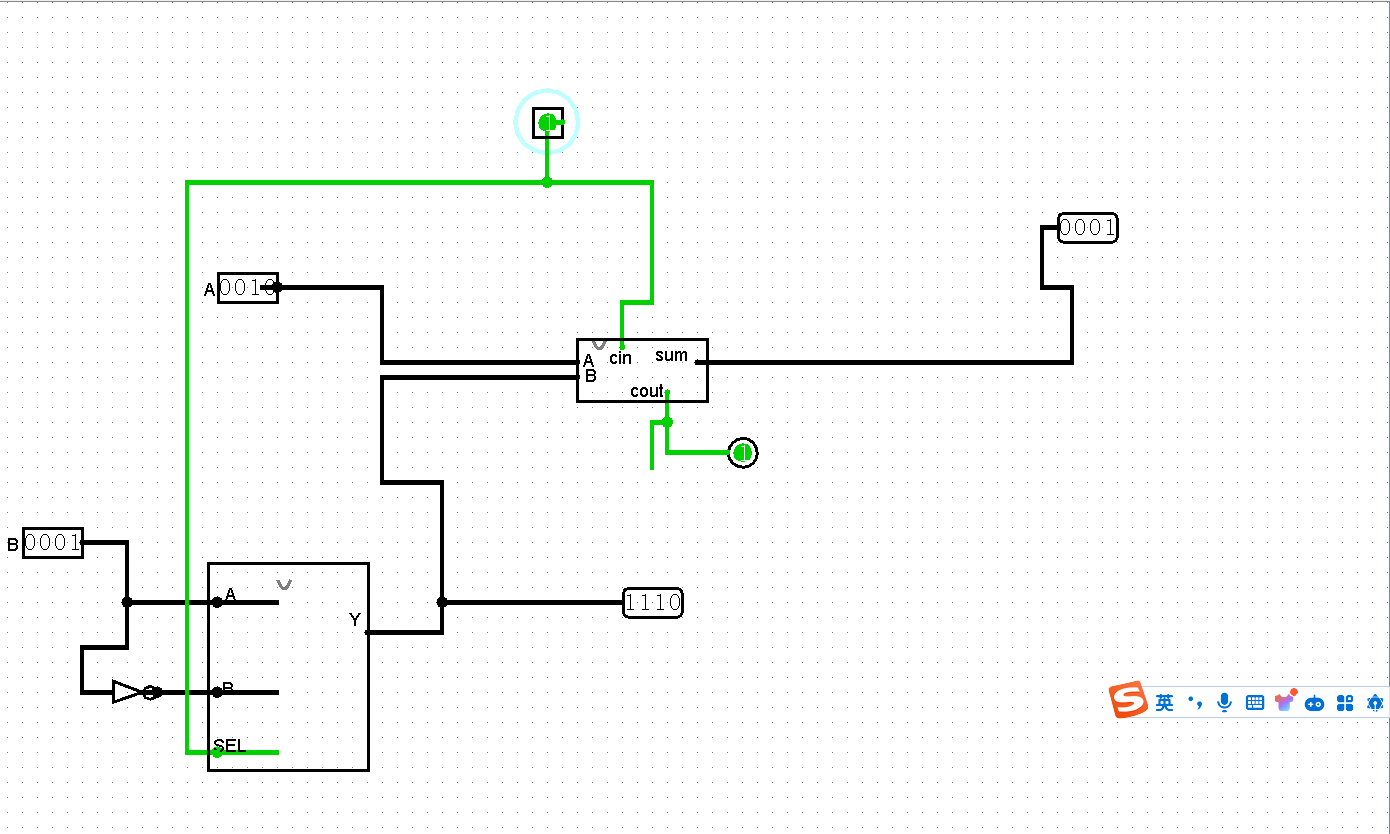

3、可控加减电路的设计(利用上节课数据选择器电路)

3.1 生成一个数字选择器

真值表:

| S | D0 | D1 | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

逻辑表达式:$Y=S⋅D_1+S⋅D_0$

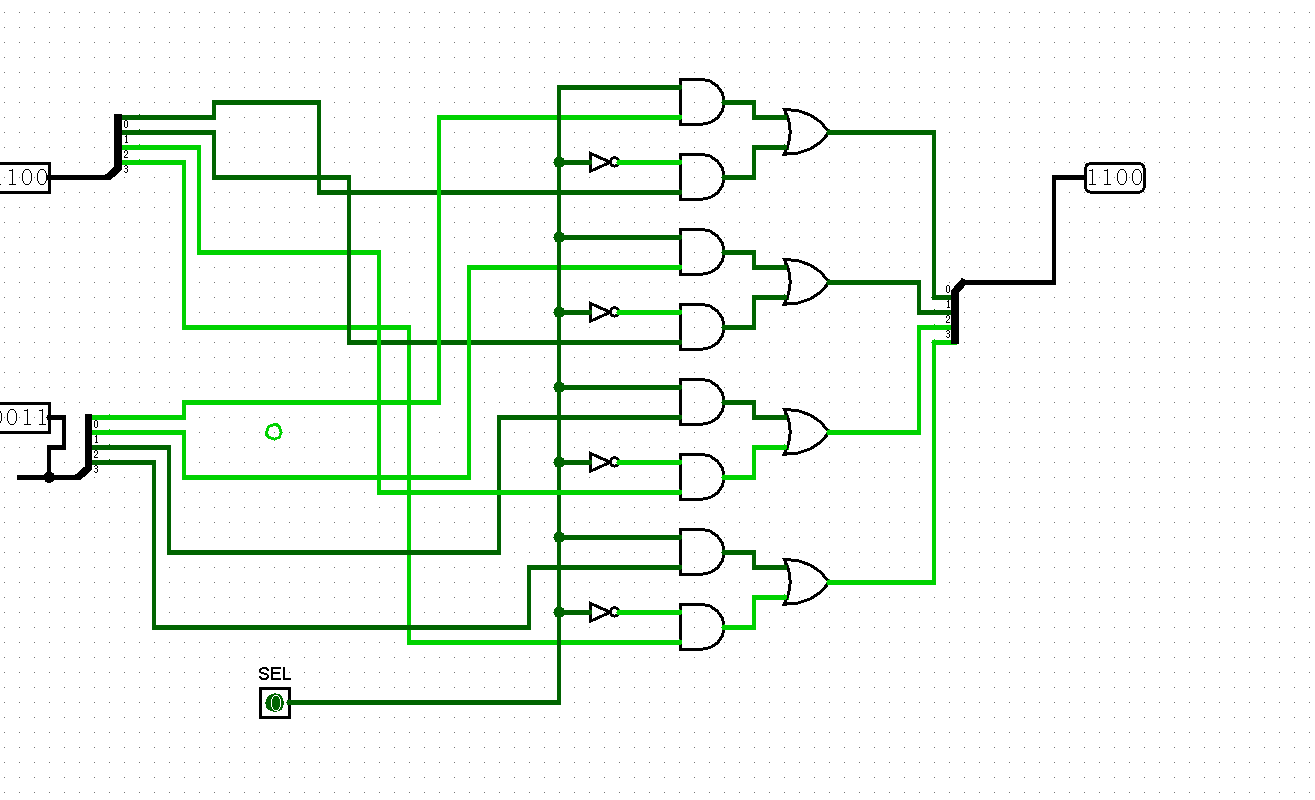

3.2 画一下

3.3 4位全加器

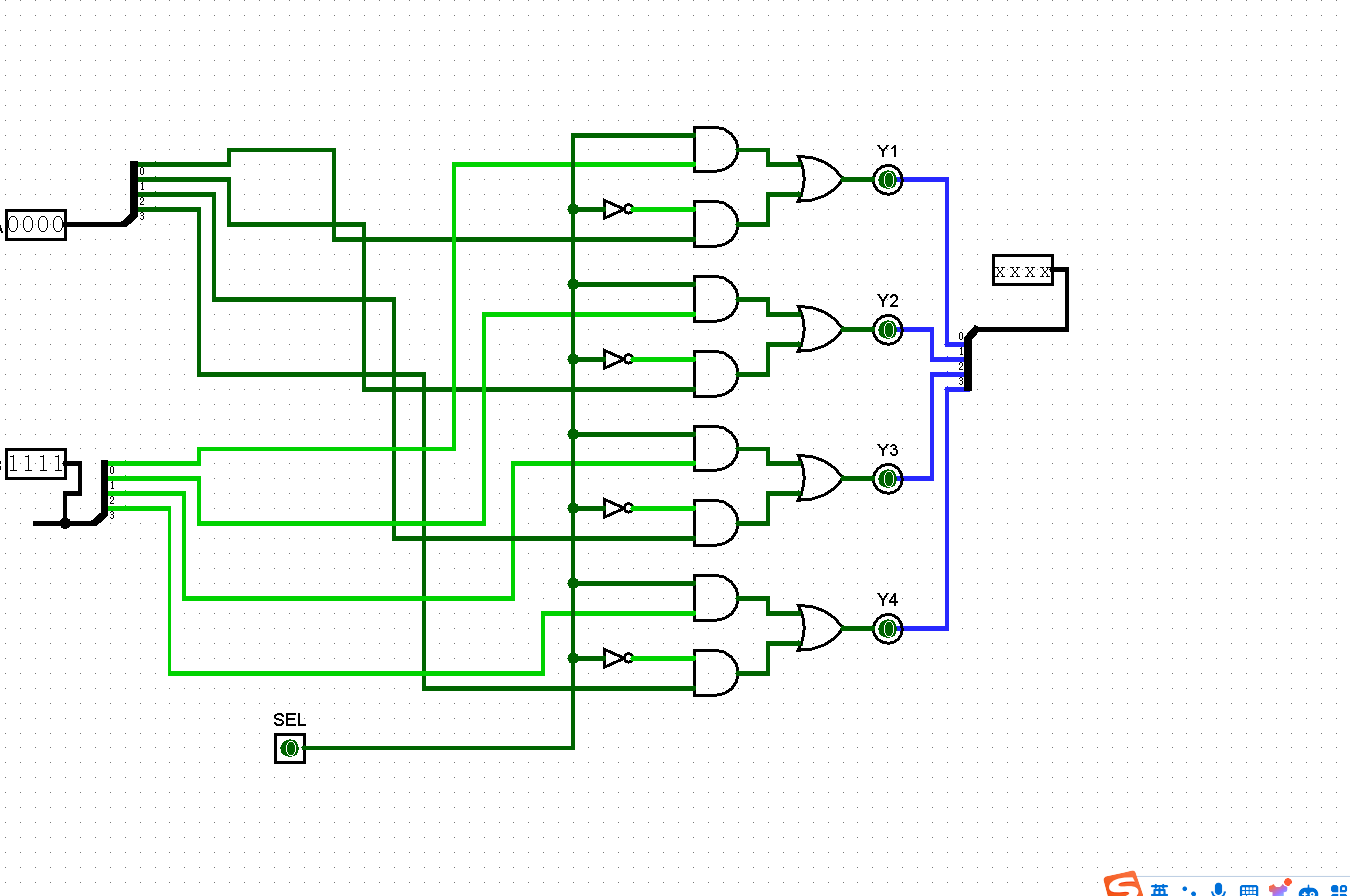

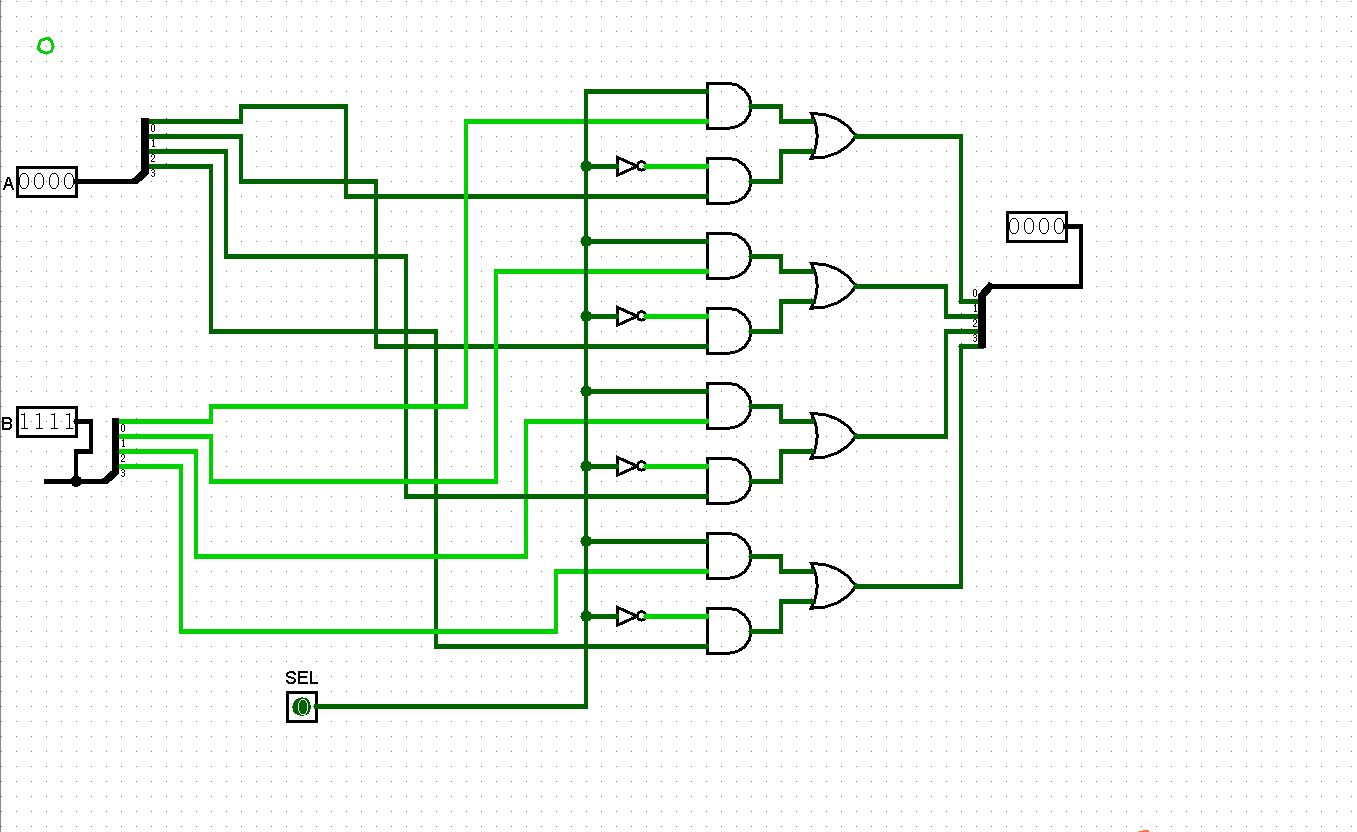

3.4 画

不兼容的位宽诶

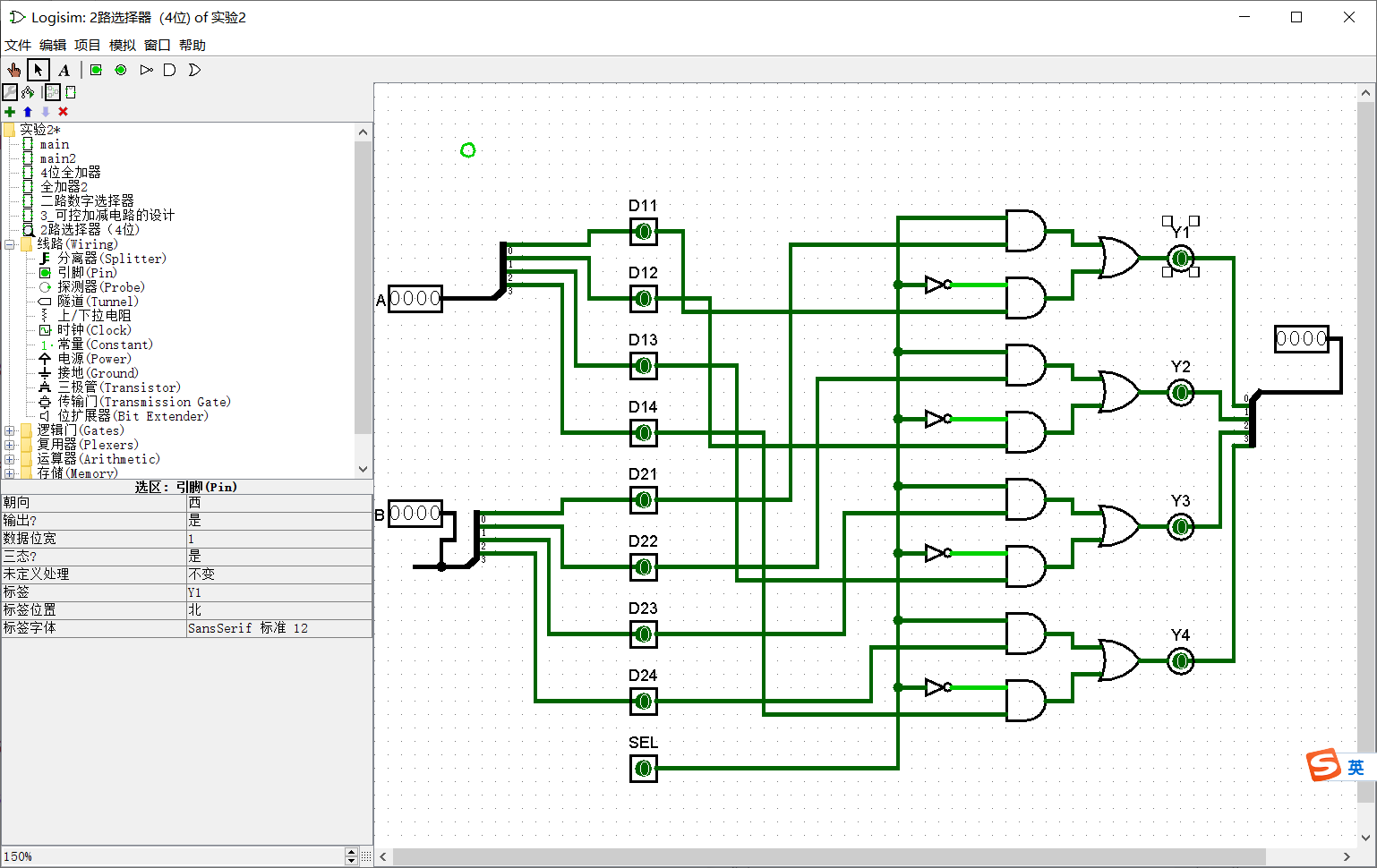

3.5 生成一个4位2路选择器

- $( Y1 = SEL \cdot D21 + \overline{SEL} \cdot D11 )$

- $( Y2 = SEL \cdot D22 + \overline{SEL} \cdot D12 )$

- $( Y3 = SEL \cdot D23 + \overline{SEL} \cdot D13 )$

- $( Y4 = SEL \cdot D24 + \overline{SEL} \cdot D14 )$

输入:

- $D_{11}$

- $D_{12}$

- $D_{13}$

- $D_{14}$

- $D_{22}$

- $D_{23}$

- $D_{24}$

- $D_{25}$

- $S_{el}$

输出:

- $Y_{1}$

- $Y_{2}$

- $Y_{3}$

- $Y_{4}$

真值表:

要命

对一下:

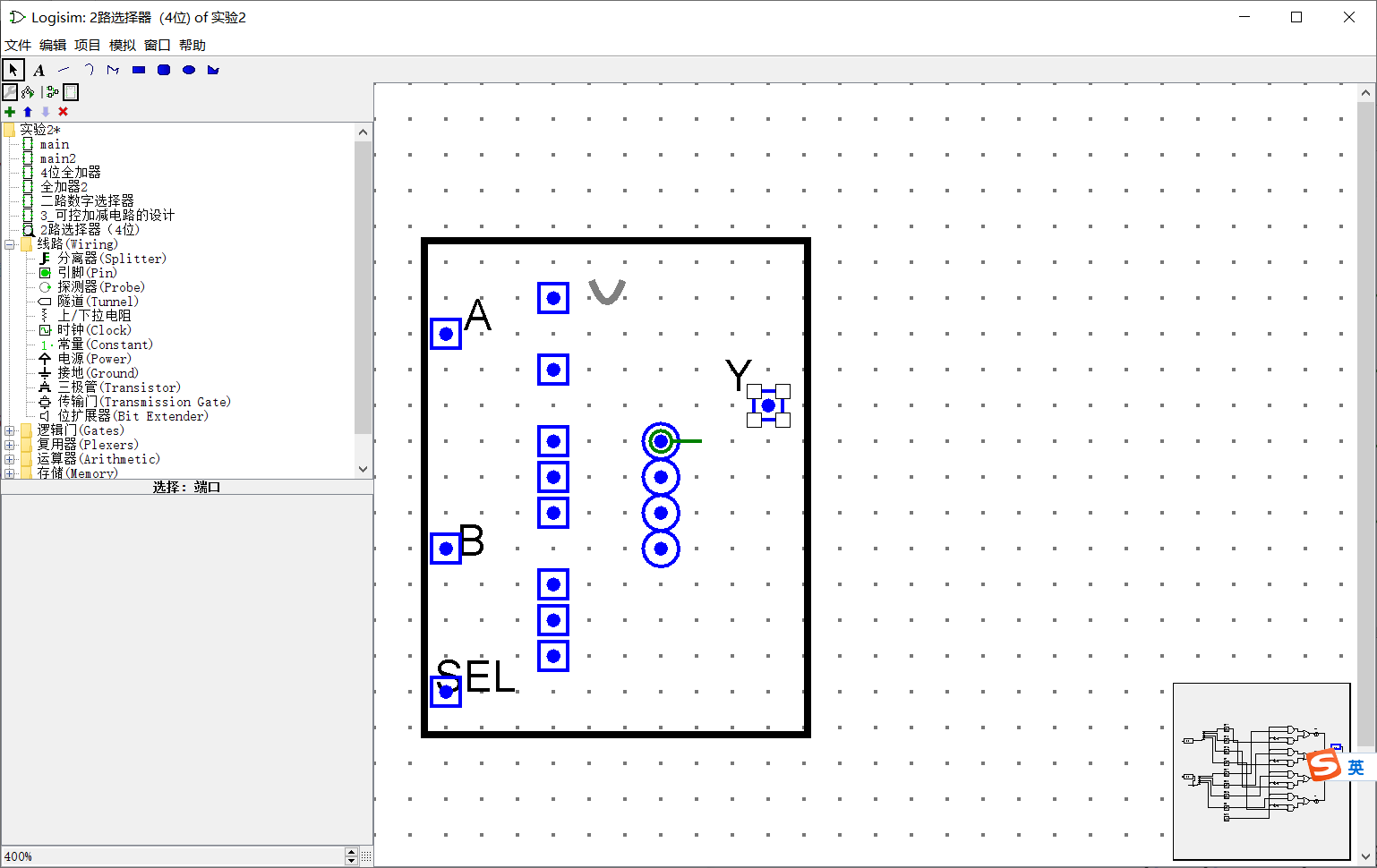

然后把这里删掉:中间多的那几个引脚删掉

这个样子:

出来啦

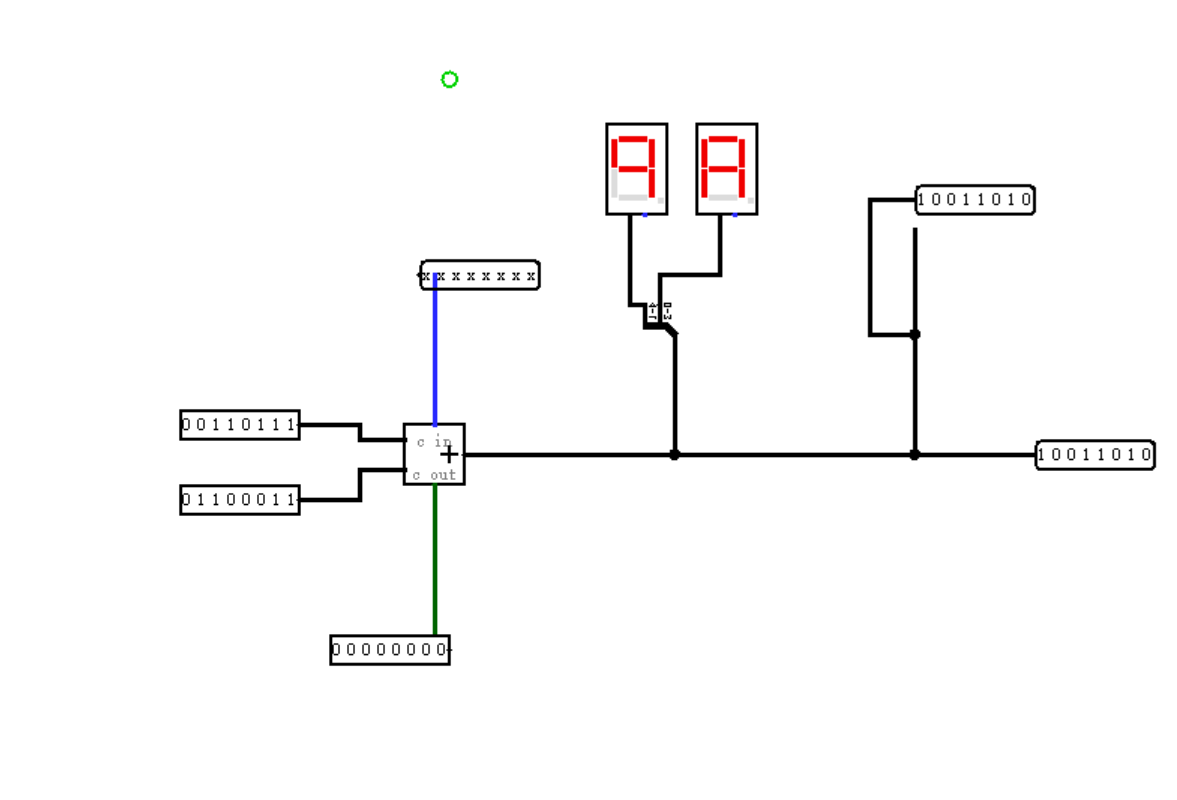

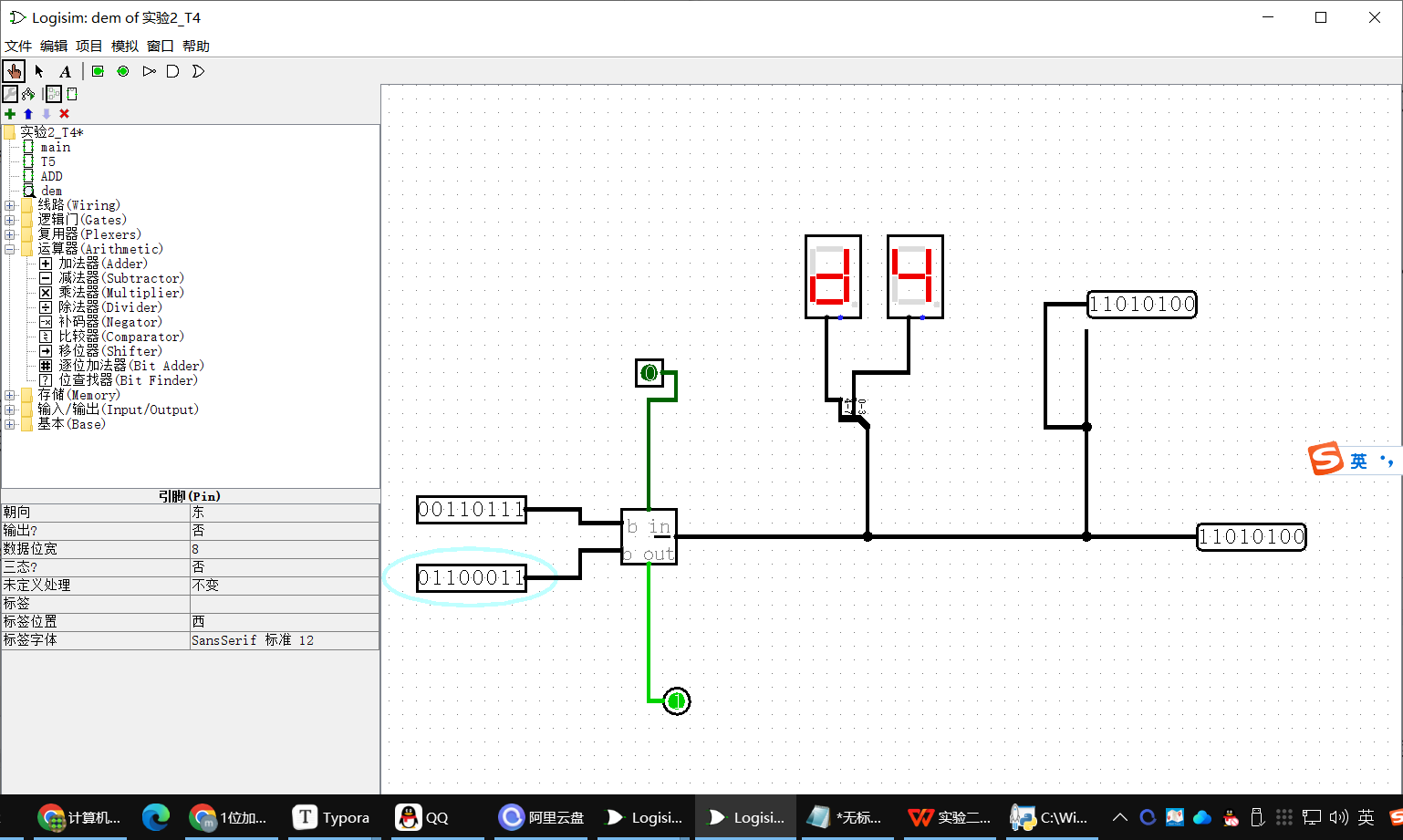

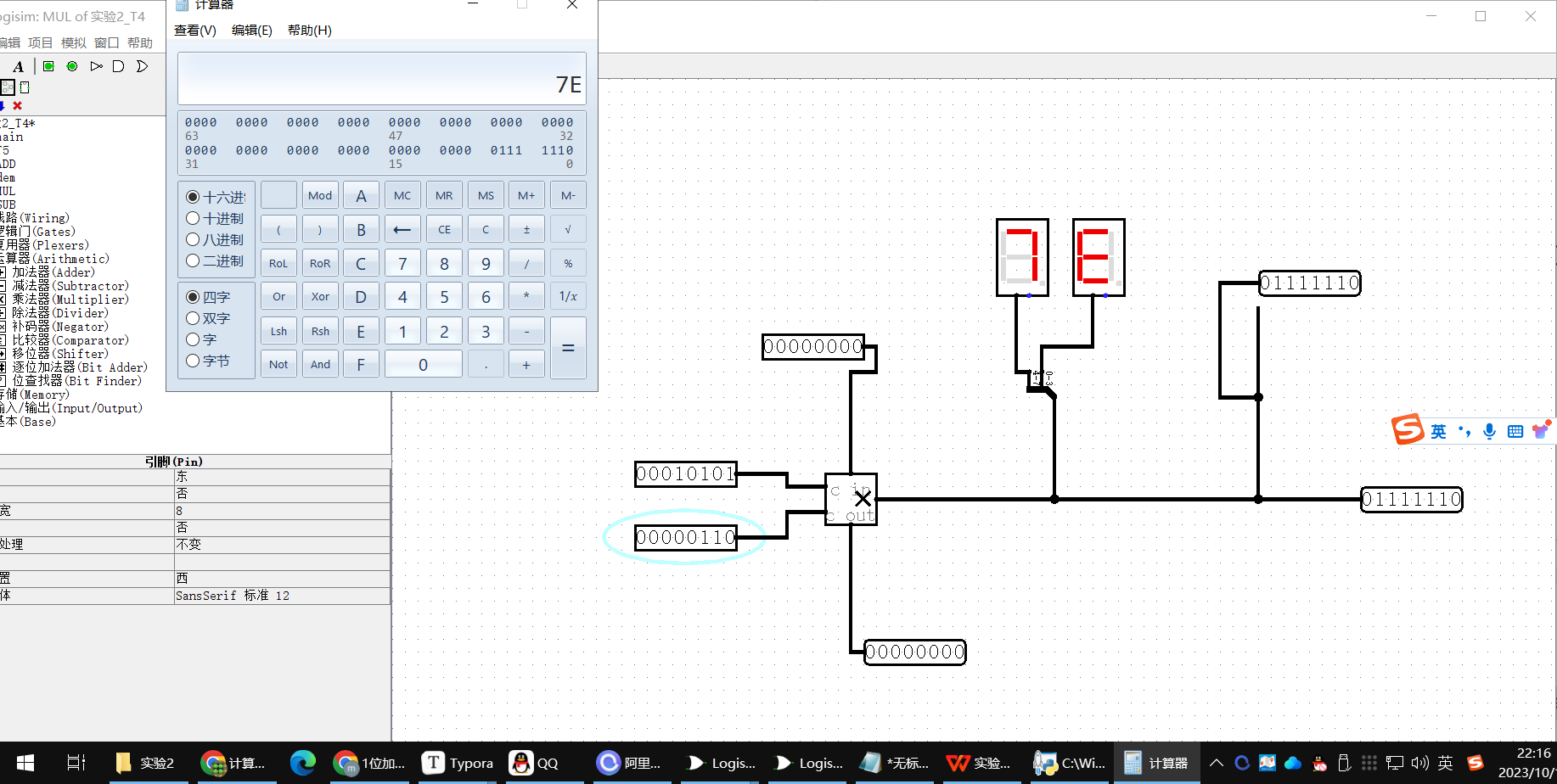

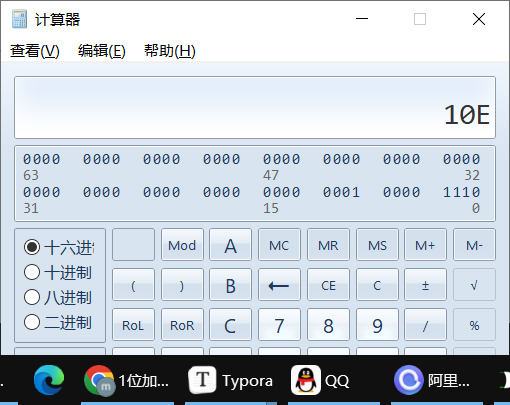

4、在Logisim中应用运算器部件设计

99+55

99-55

21*6

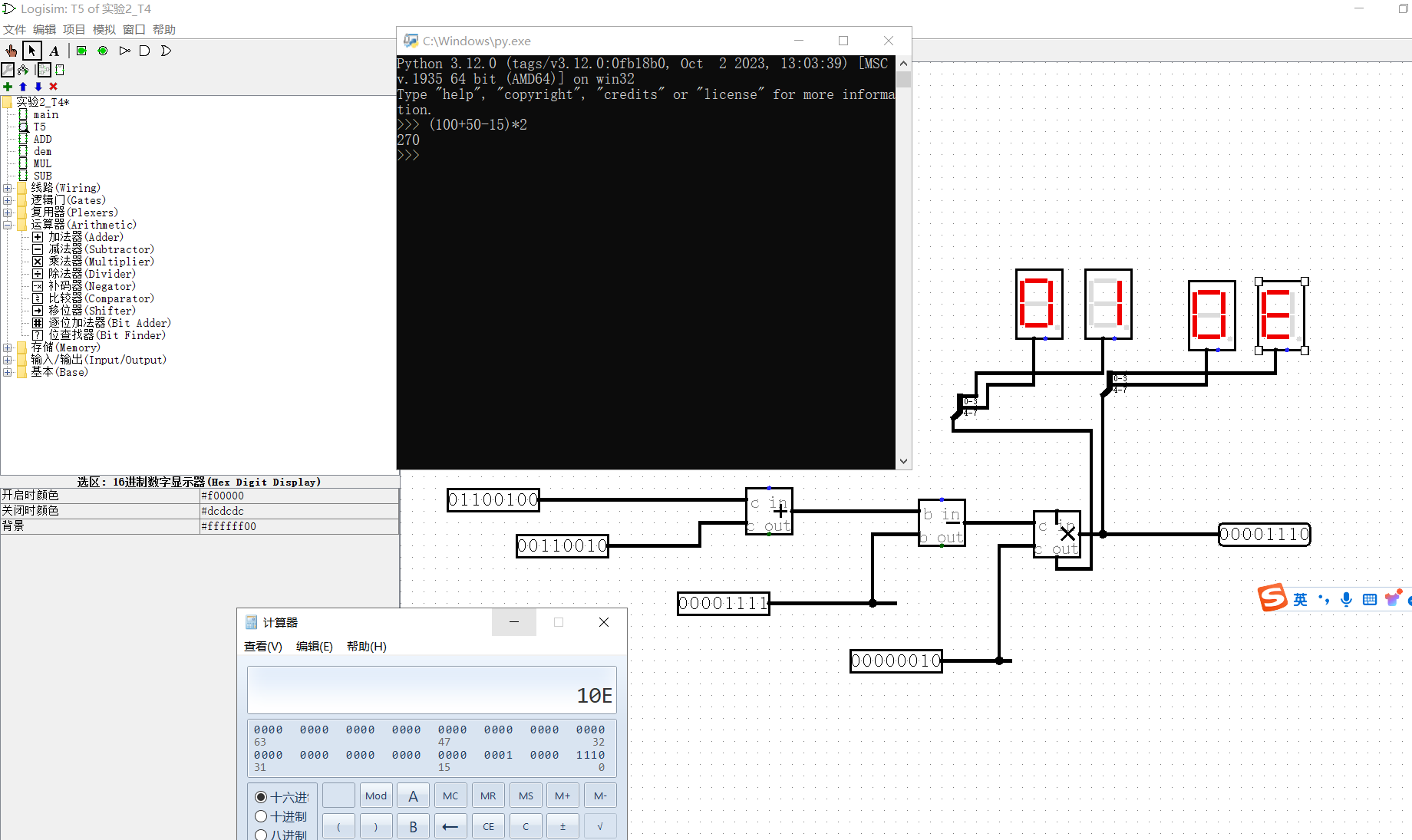

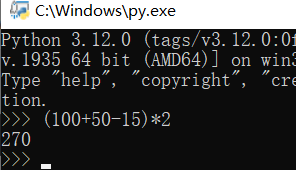

5、main电路中调用子电路实现特定四则运算

Python 3.12.0 (tags/v3.12.0:0fb18b0, Oct 2 2023, 13:03:39) [MSC v.1935 64 bit (AMD64)] on win32

Type "help", "copyright", "credits" or "license" for more information.

>>> (100+50-15)*2

270

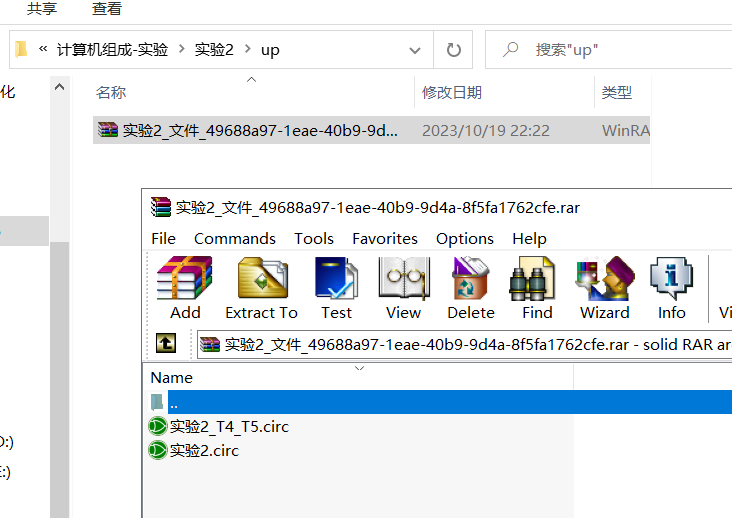

文件:

https://pic.icee.top/blog/dl_files/实验2_文件_49688a97-1eae-40b9-9d4a-8f5fa1762cfe.rar